Pin description – Rainbow Electronics MAX1143 User Manual

Page 8

MAX1142/MAX1143

14-Bit ADC, 200ksps, +5V Single-Supply

with Reference

8

_______________________________________________________________________________________

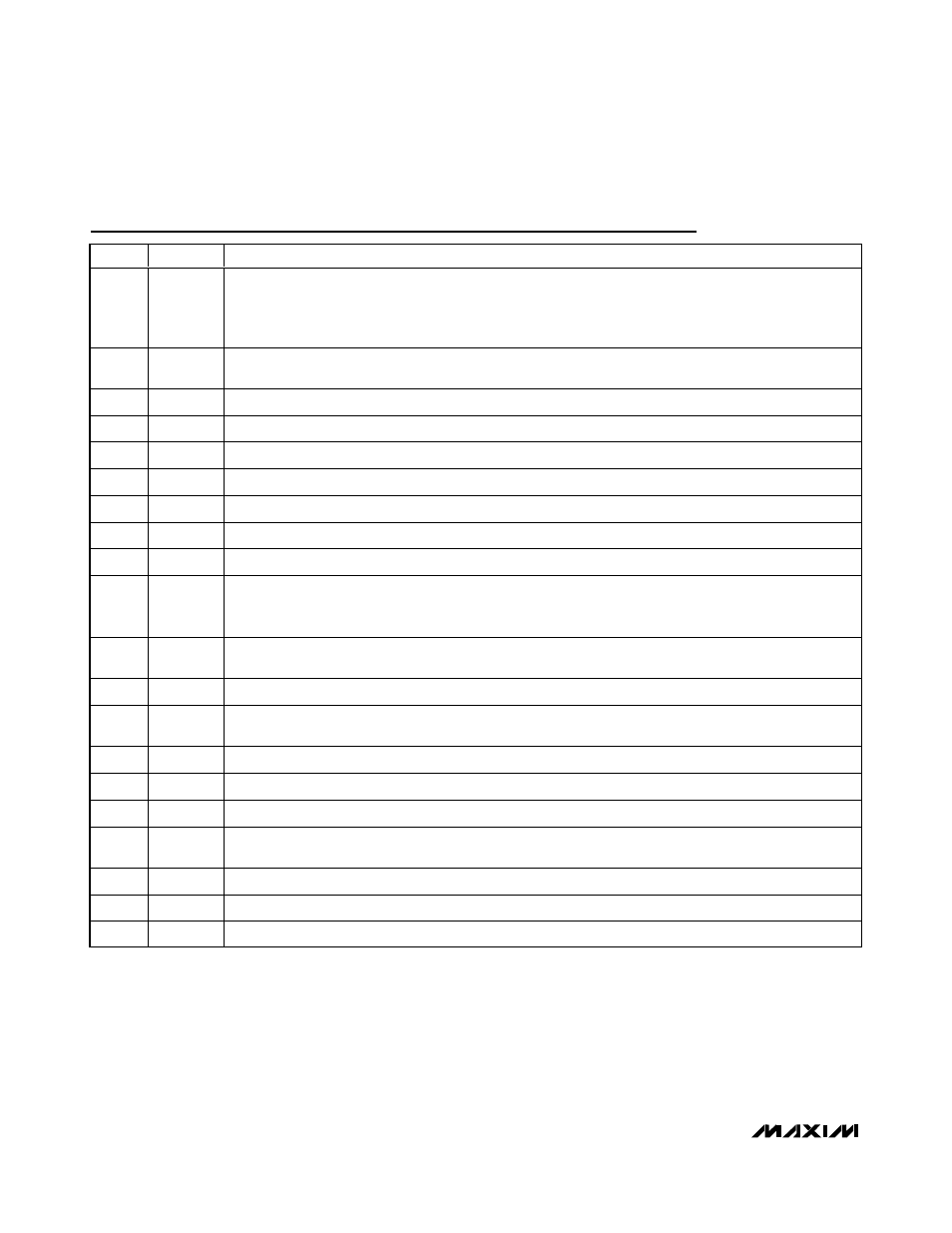

PIN

NAME

FUNCTION

1

REF

Reference Buffer Output/ADC Reference Input. Reference voltage for analog-to-digital conversion. In

internal reference mode, the reference buffer provides a +4.096V nominal output, externally adjustable at

REFADJ. In external reference mode, disable the internal buffer by pulling REFADJ to AV

DD

. Bypass to

AGND with a 2.2µF capacitor when using the internal reference.

2

REFADJ

Bandgap Reference Output/Bandgap Reference Buffer Input. Bypass to AGND with 0.22µF. When using an

external reference, connect REFADJ to AV

DD

to disable the internal bandgap reference.

3

AGND

Analog Ground. This is the primary analog ground (Star Ground).

4

AV

DD

Analog Supply 5V

±

5%. Bypass AV

DD

to AGND (pin 3) with a 0.1µF capacitor.

5

DGND

Digital Ground

6

SHDN

Shutdown Control Input. Drive

SHDN low to put the ADC in shutdown mode.

7

P2

User-Programmable Output 2

8

P1

User-Programmable Output 1

9

P0

User-Programmable Output 0

10

SSTRB

Serial Strobe Output. In internal clock mode, SSTRB goes low when the ADC begins a conversion and goes

high when the conversion is finished. In external clock mode, SSTRB pulses high for one clock period

before the MSB decision. It is high impedance when

CS is high in external clock mode.

11

DOUT

Serial Data Output. MSB first, straight binary format for unipolar input, two’s complement for bipolar input.

Each bit is clocked out of DOUT at the falling edge of SCLK.

12

RST

Reset Inp ut. D r i ve

RST l ow to p ut the d evi ce i n the p ow er - on d efaul t m od e. S ee the

P ow er - O n Reset

secti on.

13

SCLK

Serial Data Clock Input. Serial data on DIN is loaded on the rising edge of SCLK, and serial data is updated

on DOUT on the falling edge of SCLK. In external clock mode, SCLK sets the conversion speed.

14

DGND

Digital Ground. Connect to pin 5.

15

DV

DD

Digital Supply 5V

±

5%. Bypass DV

DD

to DGND (pin 14) with a 0.1µF capacitor.

16

DIN

Serial Data Input. Serial data on DIN is latched on the rising edge of SCLK.

17

CS

Chip Select Input. Drive

CS low to enable the serial interface. When CS is high, DOUT is high-impedance.

In external clock mode SSTRB is high-impedance when

CS is high.

18

CREF

Reference Buffer Bypass. Bypass CREF to AGND (pin 3) with 1µF.

19

AGND

Analog Ground. Connect pin 19 to pin 3.

20

AIN

Analog Input

Pin Description