Rainbow Electronics AT77C101B FingerChip™ User Manual

Page 10

10

AT77C101B

2150A–BIOM–02/02

.

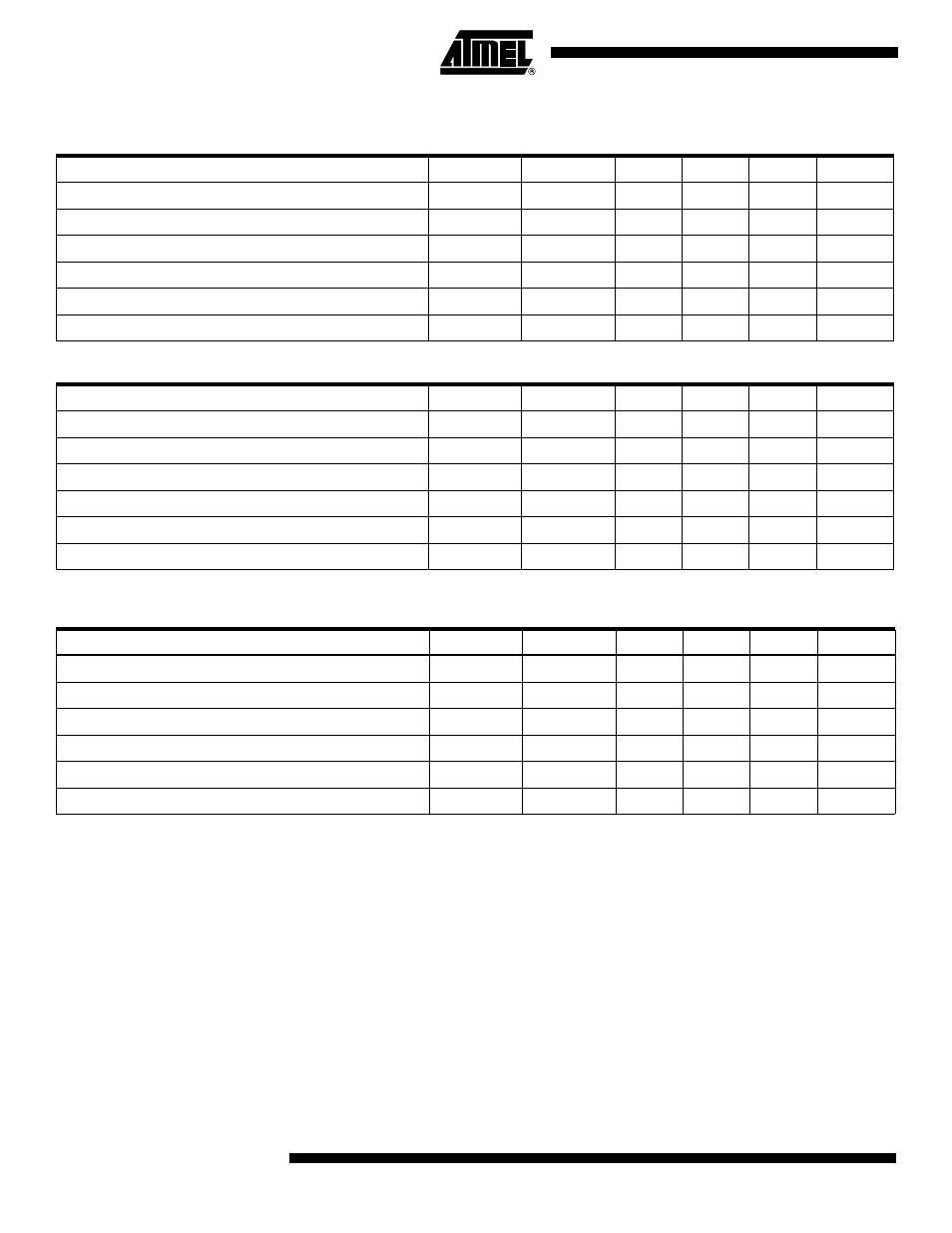

Table 7. Switching Performances. T

amb

= 25°C; F

PCLK

= 1 MHz; Duty cycle = 50%

C

load

120 pF on digital and analog outputs unless otherwise specified

Parameter

Symbol

Test Level

Min

Typ

Max

Unit

Clock frequency

f

PCLK

I

0.5

1

2

MHz

Clock pulse width (high)

t

HCLK

I

250

ns

Clock pulse width (low)

t

LCLK

I

250

ns

Clock setup time (high)/reset falling edge

t

Setup

I

0

ns

No data change

t

NOOE

IV

100

ns

Reset pulse width high

t

HRST

IV

50

ns

Table 8. 5.0V All Power Supplies = +5V

Parameter

Symbol

Test Level

Min

Typ

Max

Unit

Output delay from PCLK to ACKN rising edge

t

PLHACKN

I

90

ns

Output delay from PCLK to ACKN falling edge

t

PHLACKN

I

85

ns

Output delay from PCLK to Data output Dxi

t

PDATA

I

75

ns

Output delay from PCLK to Analog output Avx

t

PAVIDEO

I

260

ns

Output delay from OE to data high-Z

t

DATAZ

IV

25

ns

Output delay from OE to data output

t

ZDATA

IV

29

ns

Table 9. 3.3V All Power Supplies = +3.3V

Parameter

Symbol

Test Level

Min

Typ

Max

Unit

Output delay from PCLK to ACKN rising edge

t

PLHACKN

I

110

ns

Output delay from PCLK to ACKN falling edge

t

PHLACKN

I

100

ns

Output delay from PCLK to Data output Dxi

t

PDATA

I

90

ns

Output delay from PCLK to Analog output AVx

t

PAVIDEO

I

250

ns

Output delay from OE to data high-Z

t

DATAZ

IV

34

ns

Output delay from OE to data output

t

ZDATA

IV

47

ns