Dynamic range, Auxiliary dac, General-purpose i/o – Rainbow Electronics DAB-IMU-C01 User Manual

Page 16: Status and diagnostics, Table 21, Table 22, Table 24, Table 19, Table 20

ADIS16250/ADIS16255

Rev. B | Page 16 of 20

Dynamic Range

The ADIS16250/ADIS16255 provide three dynamic range

settings: ±80°/sec, ±160°/sec, and ±320°/sec. The lower

dynamic range settings (80, 160) limit the minimum filter

tap sizes in order to maintain the resolution as the maximum

rate measurements decrease. The recommended order for

programming the SENS/AVG register is (1) dynamic range

and then (2) filtering response. The contents of the

SENS/AVG register are nonvolatile.

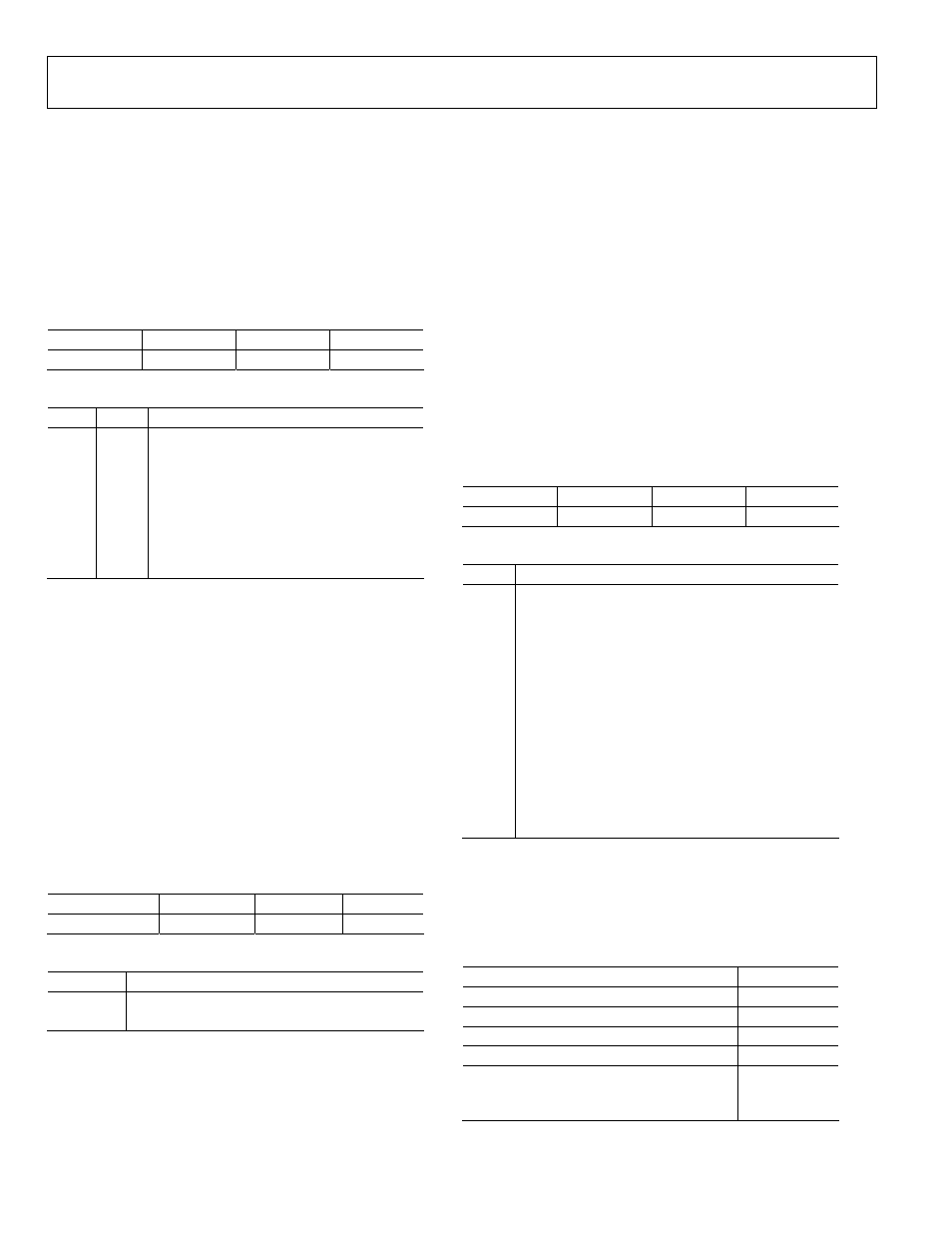

Table 19. SENS/AVG Register Definition

Address Default Format Access

0x39, 0x38

0x0402

Binary

R/W

Table 20. SENS/AVG Bit Descriptions

Bit Value

Description

15:11

Not

used

10:8

Sensitivity selection bits

100

320°/sec (default condition)

010

160°/sec, filter taps ≥ 4 (Bits[3:0] ≥ 0x02)

001

80°/sec, filter taps ≥16 (Bits[3:0] ≥ 0x04)

7:4

Not

used

3:0

Filter tap setting, M = binary number

(number of taps, N = 2

M

)

Auxiliary DAC

The auxiliary DAC provides a 12-bit level adjustment

function. The AUX_DAC register controls the operation of

this feature. It offers a rail-to-rail buffered output that has a

range of 0 V to 2.5 V. The DAC can drive its output to within

5 mV of the ground reference when it is not sinking current.

As the output approaches ground, the linearity begins to

degrade (100 LSB beginning point). As the sink current

increases, the nonlinear range increases. The DAC output

latch function, contained in the COMMAND register,

provides continuous operation while writing each byte of

this register. The contents of this register are volatile, which

means that the desired output level must be set after every

reset and power cycle event.

Table 21. AUX_DAC Register Definition

Address Default

Format

Access

0x31, 0x30

0x0000

Binary

R/W

Table 22. AUX_DAC Bit Descriptions

Bit Description

15:12 Not

used

11:0 Data

bits

General-Purpose I/O

The ADIS16250/ADIS16255 provide two general-purpose pins

that enable digital I/O control using the SPI. The GPIO_CTRL

control register establishes the configuration of these pins and

handles the SPI-to-pin controls. Each pin provides the flexibility of

both input (read) and output (write) operations. For example,

writing a 0x0202 to this register establishes Line 0 as an output and

sets its level as a one. Writing 0x0000 to this register establishes both

lines as inputs, and their status can be read through Bit 0 and Bit 1

of this register.

The digital I/O lines are also available for data-ready and alarm/error

indications. In the event of conflict, the following priority structure

governs the digital I/O configuration:

1. MSC_CTRL

2. ALM_CTRL

3. GPIO_CTRL

Table 23. GPIO_CTRL Register Definition

Address Default Format Access

0x33, 0x32

0x0000

N/A

R/W

Table 24. GPIO_CTRL Bit Descriptions

Bit

Description

15:10 Not

used

9

General-purpose I/O Line 1 polarity

1 = high

0 = low

8

General-purpose I/O Line 0 polarity

1 = high

0 = low

7:2 Not

used

1

General-purpose I/O Line 1, data direction control

1 = output

0 = input

0

General-purpose I/O Line 0, data direction control

1 = output

0 = input

STATUS AND DIAGNOSTICS

The ADIS16250/ADIS16255 provide a number of status and

diagnostic functions. Table 25 provides a summary of these

functions, along with their appropriate control registers.

Table 25. Status and Diagnostic Functions

Function Register

Data-ready I/O indicator

MSC_CTRL

Self-test, mechanical check for MEMS sensor

MSC_CTRL

Status, check for predefined error conditions

STATUS

Flash memory endurance

ENDURANCE

Alarms, configure and check for user-

specific conditions

ALM_MAG1/2

ALM_SMPL1/2

ALM_CTRL