19 test port, 20 uart, Test port – Rainbow Electronics 78M6631 User Manual

Page 13: Uart, Table 1: spi command description

DS_6631_056

78M6631 Data Sheet

Rev 1

13

Table 1: SPI Command Description

Command

Description

11xx xxxx ADDR D0 ... DN Output data on PSDO is read from RAM starting with byte at ADDR.

ADDR auto increments until PCSZ is raised.

MPU SPI interrupt is generated.

1100 0000 ADDR D0 ... DN Output data on PSDO is read from RAM starting with byte at ADDR.

ADDR auto increments until PCSZ is raised.

No MPU SPI interrupt is generated.

10xx xxxx ADDR D0 ... DN Input data on PSDI is written to RAM starting with byte at ADDR.

ADDR auto increments until PCSZ is raised.

MPU SPI interrupt is generated.

1000 0000 ADDR D0 ... DN Input data on PSDI is written to RAM starting with byte at ADDR.

ADDR auto increments until PCSZ is raised.

No MPU SPI interrupt is generated.

CMD ADDR D0 ... DN CMD and ADDR are available to the CPU in IORAM.

D0… DN are ignored.

MPU SPI interrupt is generated.

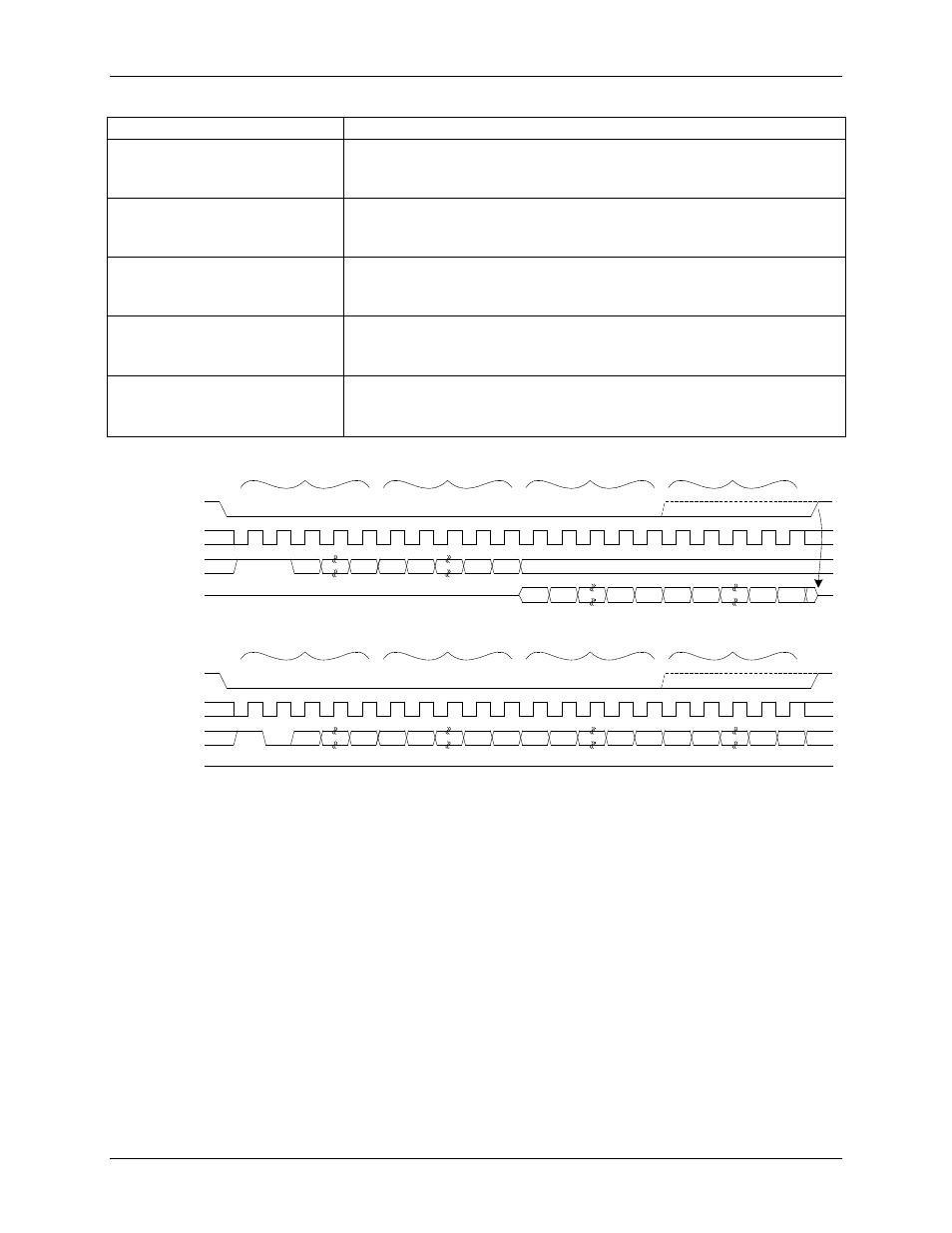

A15

A14

A1

A0

C0

0

31

x

D7

D6

D1

D0

D7

D6

D1

D0

C5

C6

C7

x

PCSZ

PSCK

PSDI

PSDO

8 bit CMD

16 bit Address

DATA[ADDR]

DATA[ADDR+1]

7

8

23

24

32

39

Extended Read . . .

SERIAL READ

A15

A14

A1

A0

C0

0

31

C5

C6

C7

x

PCSZ

PSCK

PSDI

PSDO

8 bit CMD

16 bit Address

DATA[ADDR]

DATA[ADDR+1]

7

8

23

24

32

39

Extended Write . . .

SERIAL WRITE

D7

D6

D1

D0

D7

D6

D1

D0

x

HI Z

HI Z

(From Host)

(From 6531)

(From Host)

(From 6531)

Figure 4: SPI Slave Port: Typical Read and Write Operations

Since the addresses are in 16-bit format, any type of XRAM data can be accessed: CE, MPU, or IORAM

but not SFRs or the 80515-internal register bank.

1.19 Test Port

One out of 16 digital or eight analog signals can be selected to be output on the TMUXOUT pin. Refer to

the 78M6631 Programmer’s Reference Manual for more information regarding the use of TMUXOUT.

1.20 UART

The 78M6631 includes one UART (UART0) that can be programmed to communicate with a variety of

external devices. The UART is a dedicated 2-wire serial interfaces (no hardware flow

control/handshaking), which can communicate at rates up to 38,400 bps. All UART transfers are

programmable for parity enable, parity, 2 stop bits/1 stop bit and XON/XOFF options for variable

communication baud rates from 300 to 38,400 bps. Refer to the 78M6631 Programmer’s Reference

Manual for more information regarding the use of the UART resources.