Ds1374 i, Power-up/power-down characteristics – Rainbow Electronics DS1374 User Manual

Page 5

DS1374

I

2

C, 32-Bit Binary Counter Watchdog RTC with

Trickle Charger and Reset Input/Output

_____________________________________________________________________

5

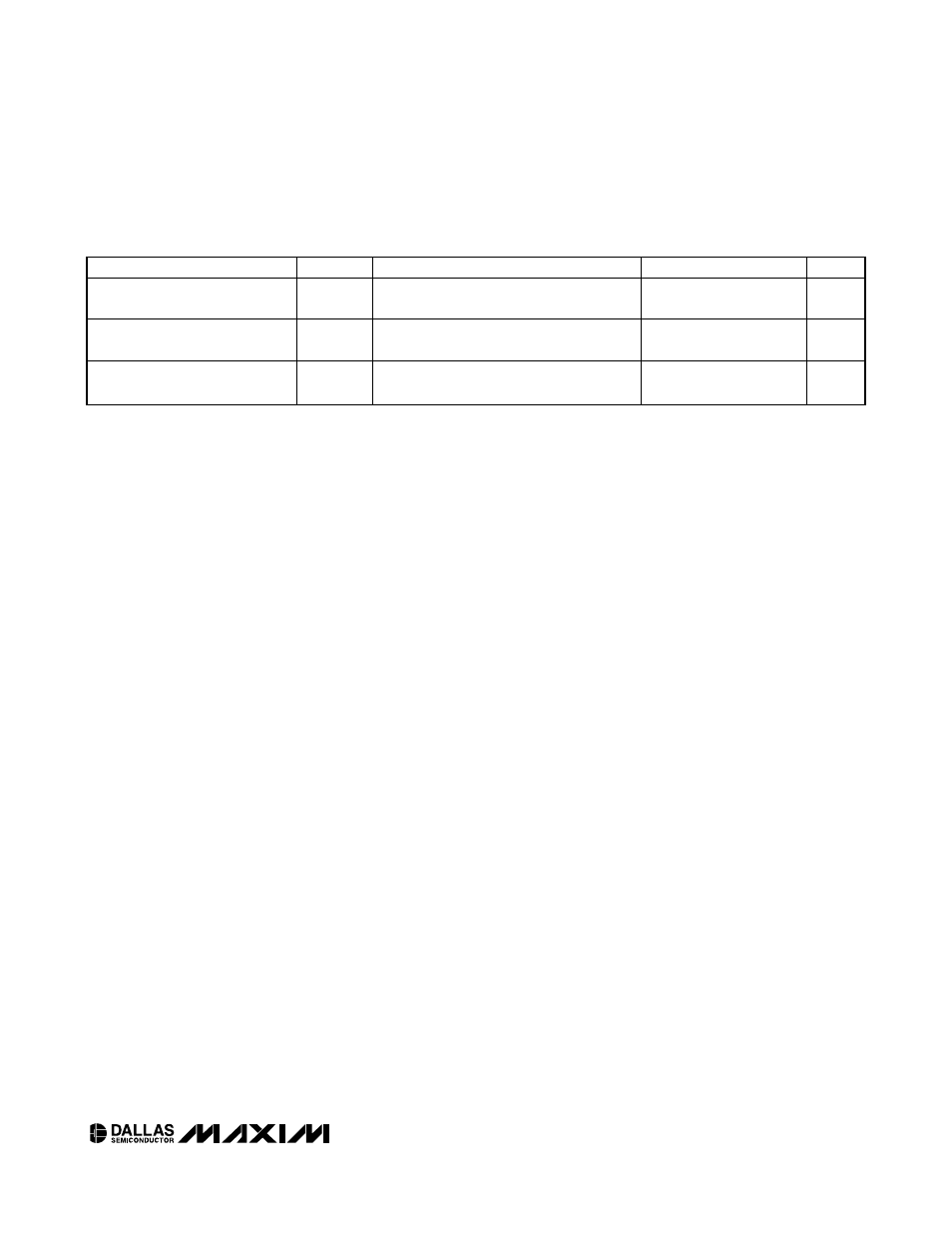

POWER-UP/POWER-DOWN CHARACTERISTICS

(T

A

= -40°C to +85°C) (Figure 3)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

V

CC

Detect to Recognize Inputs

(V

CC

Rising)

t

RPU

(Note 23)

250

ms

V

CC

Fall Time; V

PF(MAX)

to

V

PF(MIN)

t

F

300

µs

V

CC

Rise Time; V

PF(MIN)

to

V

PF(MAX)

t

R

0

µs

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when the device is in write protection.

Note 1:

Limits at -40°C are guaranteed by design and not production tested.

Note 2:

All voltages are referenced to ground.

Note 3:

V

BACKUP

should not exceed V

CC

MAX or 3.7V, whichever is greater.

Note 4:

The use of the 250

Ω trickle-charge resistor is not allowed at V

CC

> 3.63V and should not be enabled.

Note 5:

Measured at V

CC

= typ, V

BACKUP

= 0V, register 09h = A5h.

Note 6:

Measured at V

CC

= typ, V

BACKUP

= 0V, register 09h = A6h.

Note 7:

Measured at V

CC

= typ, V

BACKUP

= 0V, register 09h = A7h.

Note 8:

SCL only.

Note 9:

SDA and SQW and

INT.

Note 10: The

RST pin has an internal 50k

Ω pullup resistor to V

CC

.

Note 11: Trickle charger disabled.

Note 12: I

CCA

—SCL clocking at max frequency = 400kHz.

Note 13: Specified with I

2

C bus inactive.

Note 14: Measured with a 32.768kHz crystal attached to the X1 and X2 pins.

Note 15: WDSTR = 1. BBSQW = 1 is required for operation when V

CC

is below the power-fail trip point (or absent).

Note 16: C

B

—total capacitance of one bus line in pF.

Note 17: After this period, the first clock pulse is generated.

Note 18: The maximum t

HD:DAT

only has to be met if the device does not stretch the low period (t

LOW

) of the SCL signal.

Note 19: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to as the V

IHMIN

of the SCL sig-

nal) to bridge the undefined region of the falling edge of SCL.

Note 20: A fast-mode device can be used in a standard-mode system, but the requirement t

SU:DAT

≥ to 250ns must be met. This is

automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low

period of the SCL signal, it must output the next data bit to the SDA line t

R

max + t

SU:DAT

= 1000 + 250 = 1250ns before

the SCL line is released.

Note 21: Guaranteed by design. Not production tested.

Note 22: The parameter t

OSF

is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of

0V

≤ V

CC

≤ V

CC MAX

and 1.3V

≤ V

BACKUP

≤ 3.7V.

Note 23: This delay applies only if the oscillator is enabled and running. If the

EOSC bit is 1, the startup time of the oscillator is

added to this delay.