3 the window watchdog (ptrig, ntrig and nres) – Rainbow Electronics ATA6626 User Manual

Page 4

4

4970A–AUTO–01/07

ATA6621/22/24 Development Board

2.3

The Window Watchdog (PTRIG, NTRIG and NRES)

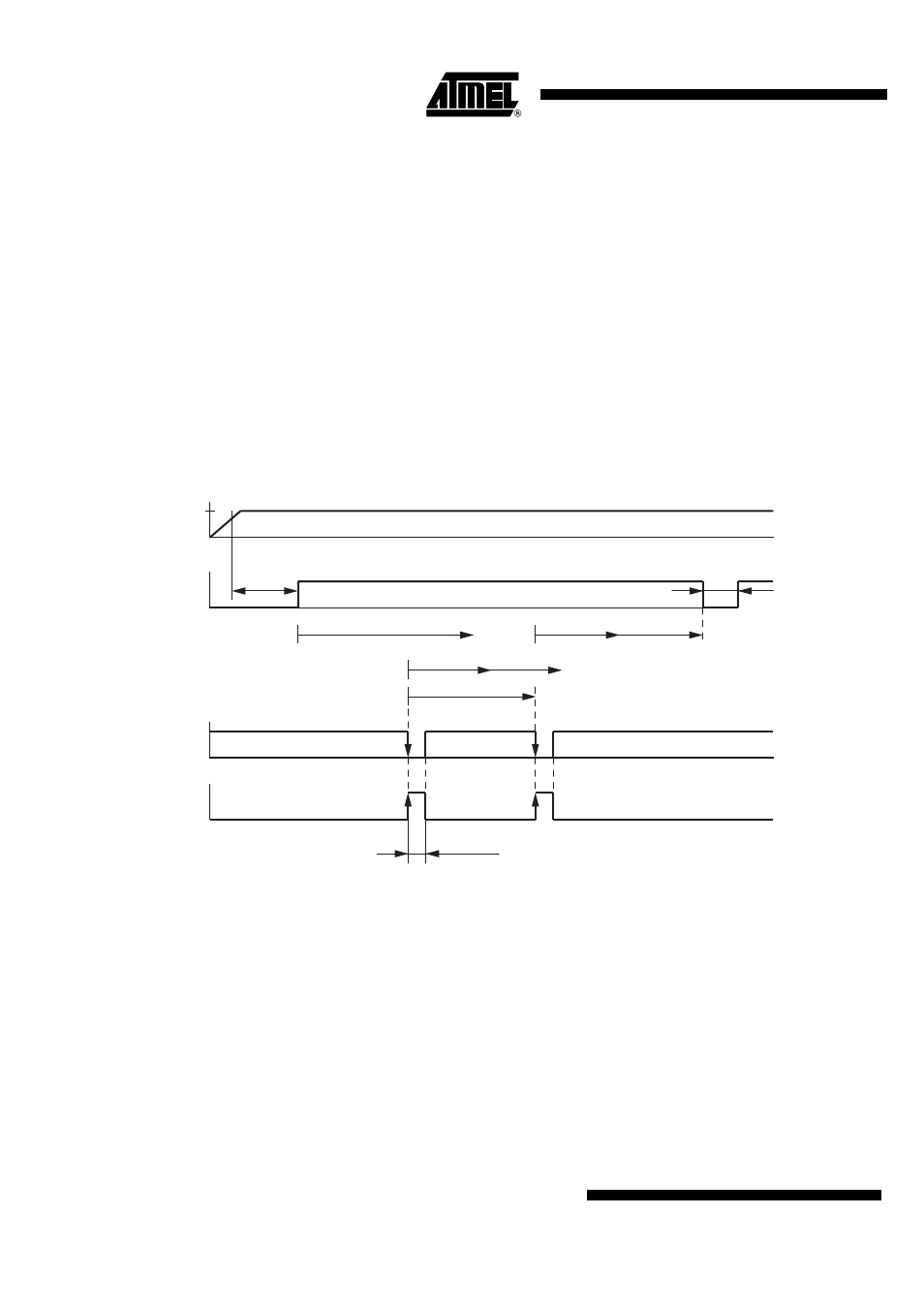

The watchdog anticipates a trigger signal from the microcontroller at the NTRIG input (nega-

tive edge) within a defined time window. The ATA6621 has an additional PTRIG input, so it is

also possible to trigger the watchdog with a positive edge. If no correct trigger signal is

received, a reset signal will be generated at the NRES output. During Silent or Sleep Mode the

watchdog is switched off to reduce current consumption.

The minimum time for the first watchdog pulse is required after the undervoltage reset at the

NRES pin disappears and is defined as lead time t

d

.

The timing basis of the watchdog is provided by the internal oscillator, whose time period t

OSC

is adjustable via the external resistor R3 at the pin WD_OSC. For the ATA6621, the voltage at

this pin is 2.5V, for the ATA6622 and ATA6624 it is 1.23V (see

through

). Due to these different voltages at the devices, the resulting timings are

also different. There is a resistor R3 with a value of 51 k

Ω

mounted on the development board,

which results in the following timing sequence for the ATA6621:

Figure 2-1.

Timing Sequence with R3 = 51 k

Ω

at the ATA6621

t

nres

= 1.9 ms

Undervoltage Reset

Watchdog Reset

t

reset

= 10 ms

t

1

= 10 ms

t

trigg

> 3 µs

t

2

= 10.5 ms

t

2

t

1

t

wd

t

d

= 49 ms

V

CC

= 5V

PTRIG

NTRIG

NRES