Specification definitions, Figure 1 – Rainbow Electronics ADC081000 User Manual

Page 10

Specification Definitions

APERTURE (SAMPLING) DELAY is that time required after

the fall of the clock input for the sampling switch to open. The

Sample/Hold circuit effectively stops capturing the input sig-

nal and goes into the “hold” mode the aperture delay time

(t

AD

) after the clock goes low.

APERTURE JITTER (t

AJ

) is the variation in aperture delay

from sample to sample. Aperture jitter shows up as input

noise.

CLOCK DUTY CYCLE is the ratio of the time that the clock

wave form is at a logic high to the total time of one clock

period.

DIFFERENTIAL NON-LINEARITY (DNL) is the measure of

the maximum deviation from the ideal step size of 1 LSB.

Measured at 1 GSPS with a ramp input.

EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE

BITS) is another method of specifying Signal-to-Noise and

Distortion Ratio, or SINAD. ENOB is defined as (SINAD −

1.76) / 6.02 and says that the converter is equivalent to a

perfect ADC of this (ENOB) number of bits.

FULL POWER BANDWIDTH (FPBW) is a measure of the

frequency at which the reconstructed output fundamental

drops 3 dB below its low frequency value for a full scale

input.

GAIN ERROR is the deviation from the ideal slope of the

transfer function. It can be calculated from Offset and Full-

Scale Errors:

–

PGE = OE − PFSE

–

NGE = −(OE − NFSE) = NFSE − OE

–

Gain Error = NFSE − PFSE = PGE + NGE

where PGE is Positive Gain Error, NGE is Negative Gain

Error, OE is Offset Error, PFSE is Positive Full-Scale Error

and NFSE is Negative Full-Scale Error.

INTEGRAL NON-LINEARITY (INL) is a measure of the

deviation of each individual code from a straight line through

the input to output transfer function. The deviation of any

given code from this straight line is measured from the

center of that code value. The best fit method is used.

INTERMODULATION DISTORTION (IMD) is the creation of

additional spectral components as a result of two sinusoidal

frequencies being applied to the ADC input at the same time.

it is defined as the ratio of the power in the second and third

order intermodulation products to the power in one of the

original frequencies. IMD is usually expressed in dBFS.

LSB (LEAST SIGNIFICANT BIT) is the bit that has the

smallest value or weight of all bits. This value is

V

FS

/ 2

n

where V

FS

is the differential full-scale amplitude of 600 mV

or 800 mV as set by the FSR input and "n" is the ADC

resolution in bits, which is 8 for the ADC081000.

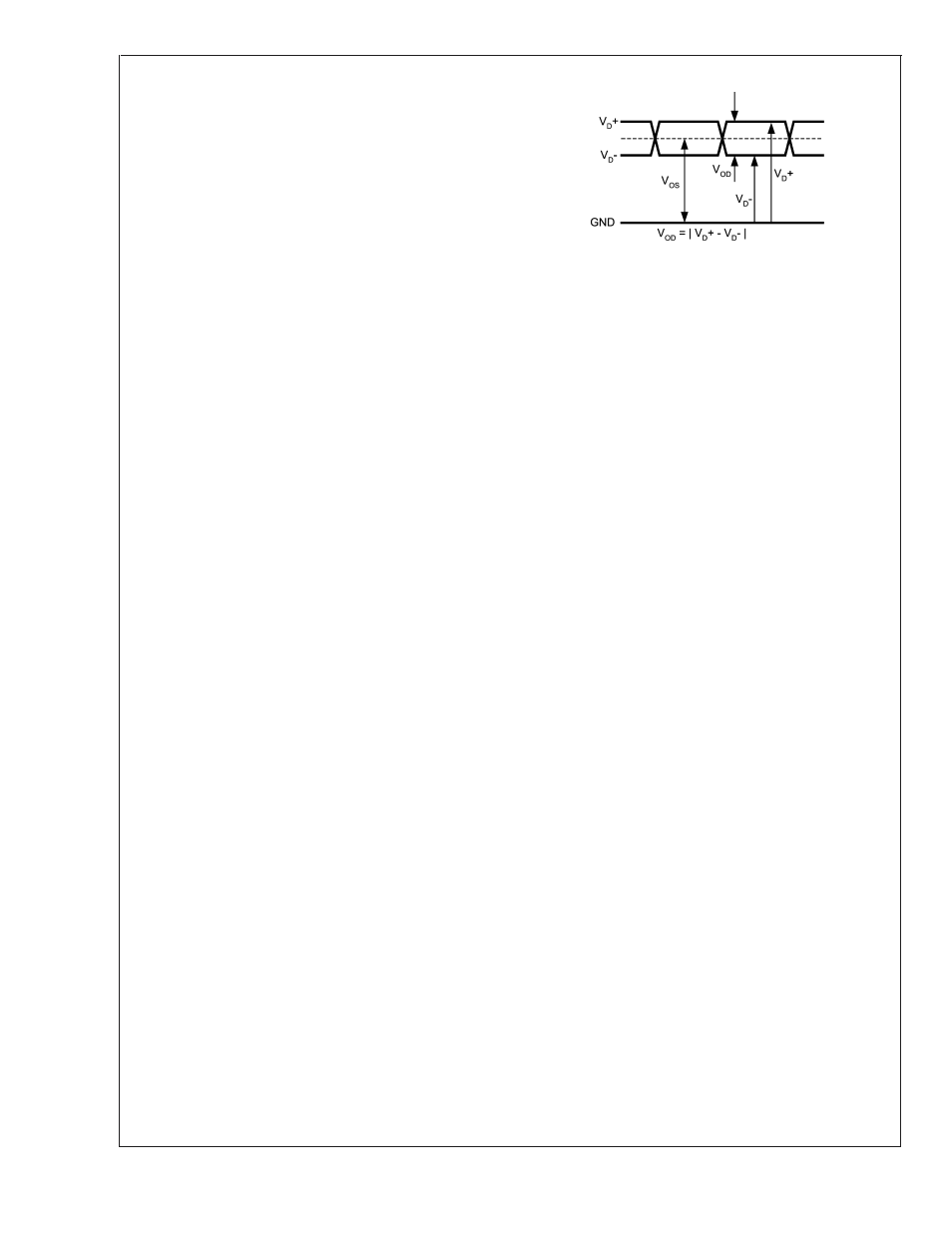

LVDS DIFFERENTIAL OUTPUT VOLTAGE (V

OD

) is this

absolute value of the difference between the V

D

+ and V

D

−

outputs, each measured with respect to Ground.

LVDS OUTPUT OFFSET VOLTAGE (V

OS

) is the midpoint

between the the D+ and D− pins’ output voltages; i.e.,

[ (VD+) + (VD−) ] / 2.

MISSING CODES are those output codes that are skipped

and will never appear at the ADC outputs. These codes

cannot be reached with any input value.

MSB (MOST SIGNIFICANT BIT) is the bit that has the

largest value or weight. Its value is one half of full scale.

NEGATIVE FULL-SCALE ERROR is a measure of how far

the last code transition is from the ideal 1/2 LSB above a

differential −800 mV with the FSR pin high, or 1/2 LSB above

a differential −600 mV with the FSR pin low. For the

ADC081000 the reference voltage is assumed to be ideal, so

this error is a combination of full-scale error and reference

voltage error.

OFFSET ERROR (V

OFF

) is a measure of how far the mid-

scale point is from the ideal zero voltage differential input.

OUTPUT DELAY (t

OD

) is the time delay after the falling edge

of the DCLK before the data update is present at the output

pins.

OVER-RANGE RECOVERY TIME is the time required after

the differential input voltages goes from

±

1.2V to 0V for the

converter to recover and make a conversion with its rated

accuracy.

PIPELINE DELAY (LATENCY) is the number of clock cycles

between initiation of conversion and when that data is pre-

sented to the output driver stage. New data is available at

every clock cycle, but the data lags the conversion by the

Pipeline Delay plus the t

OD

.

POSITIVE FULL-SCALE ERROR (PFSE) is a measure of

how far the last code transition is from the ideal 1-1/2 LSB

below a differential +800 mV with the FSR pin high, or 1-1/2

LSB below a differential +600 mV with the FSR pin low. For

the ADC081000 the reference voltage is assumed to be

ideal, so this error is a combination of full-scale error and

reference voltage error.

POWER SUPPLY REJECTION RATIO (PSRR) can be one

of two specifications. PSRR1 (DC PSRR) is the ratio of the

change in offset error that results from a power supply

voltage change from 1.8V to 2.0V. PSRR2 (AC PSRR) is a

measure of how well an a.c. signal riding upon the power

supply is rejected from the output and is measured with a

248 MHz, 50 mV

P-P

signal riding upon the power supply. It is

the ratio of the output amplitude of that signal at the output to

its amplitude on the power supply pin. PSRR is expressed in

dB.

20068190

FIGURE 1.

ADC081000

www.national.com

10