Instruction set summary – Rainbow Electronics AT90S1200 User Manual

Page 63

63

AT90S1200

0838H–AVR–03/02

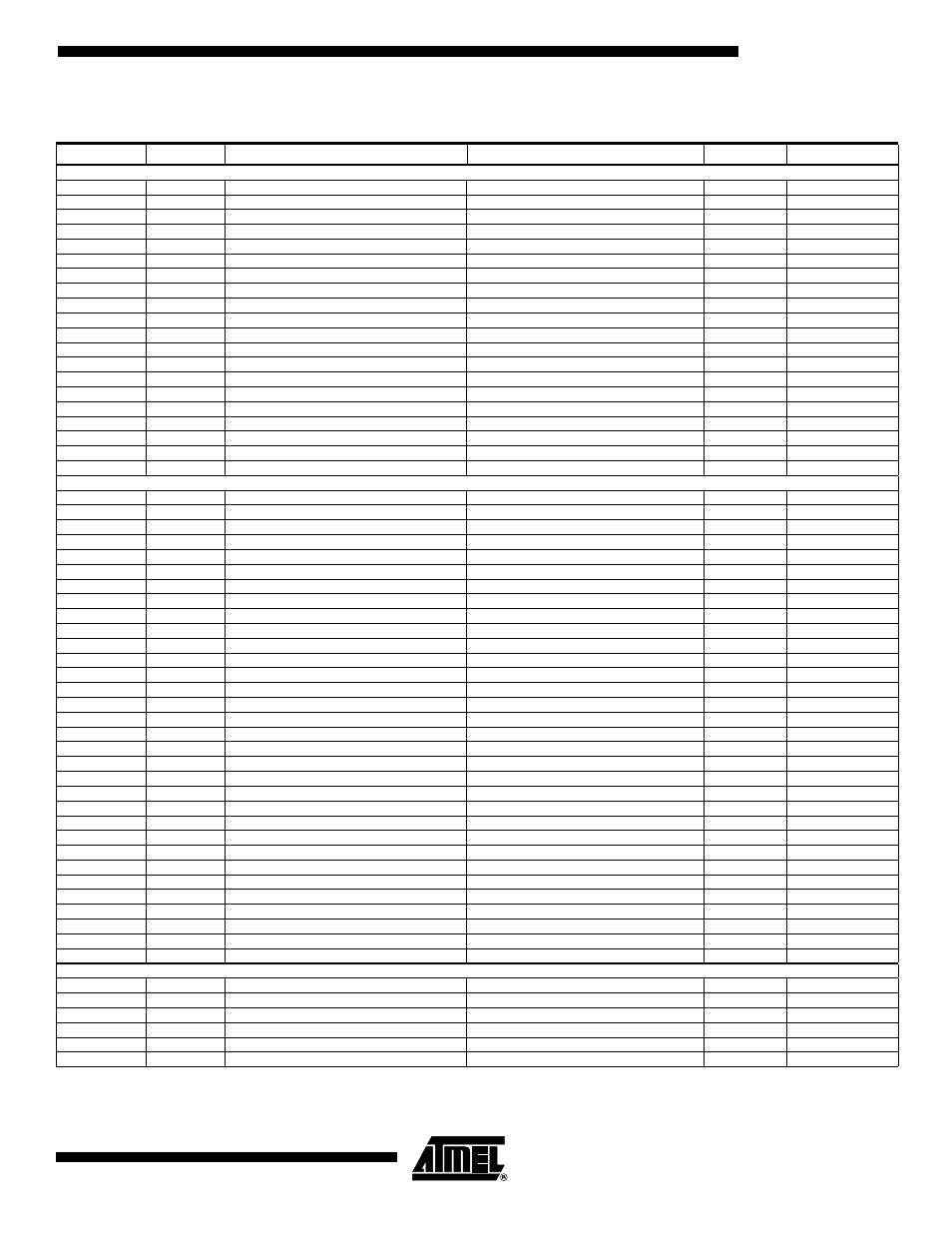

Instruction Set Summary

Mnemonic

Operands

Description

Operation

Flags

# Clocks

ARITHMETIC AND LOGIC INSTRUCTIONS

ADD

Rd, Rr

Add Two Registers

Rd

←

Rd + Rr

Z,C,N,V,H

1

ADC

Rd, Rr

Add with Carry Two Registers

Rd

←

Rd + Rr + C

Z,C,N,V,H

1

SUB

Rd, Rr

Subtract Two Registers

Rd

←

Rd - Rr

Z,C,N,V,H

1

SUBI

Rd, K

Subtract Constant from Register

Rd

←

Rd - K

Z,C,N,V,H

1

SBC

Rd, Rr

Subtract with Carry Two Registers

Rd

←

Rd - Rr - C

Z,C,N,V,H

1

SBCI

Rd, K

Subtract with Carry Constant from Reg.

Rd

←

Rd - K - C

Z,C,N,V,H

1

AND

Rd, Rr

Logical AND Registers

Rd

←

Rd

•

Rr

Z,N,V

1

ANDI

Rd, K

Logical AND Register and Constant

Rd

←

Rd

•

K

Z,N,V

1

OR

Rd, Rr

Logical OR Registers

Rd

←

Rd v Rr

Z,N,V

1

ORI

Rd, K

Logical OR Register and Constant

Rd

←

Rd v K

Z,N,V

1

EOR

Rd, Rr

Exclusive OR Registers

Rd

←

Rd

⊕ Rr

Z,N,V

1

COM

Rd

One’s Complement

Rd

←

$FF - Rd

Z,C,N,V

1

NEG

Rd

Two’s Complement

Rd

←

$00 - Rd

Z,C,N,V,H

1

SBR

Rd, K

Set Bit(s) in Register

Rd

←

Rd v K

Z,N,V

1

CBR

Rd, K

Clear Bit(s) in Register

Rd

←

Rd

•

(FFh - K)

Z,N,V

1

INC

Rd

Increment

Rd

←

Rd + 1

Z,N,V

1

DEC

Rd

Decrement

Rd

←

Rd - 1

Z,N,V

1

TST

Rd

Test for Zero or Minus

Rd

←

Rd

•

Rd Z,N,V

1

CLR

Rd

Clear Register

Rd

←

Rd

⊕ Rd

Z,N,V

1

SER

Rd

Set Register

Rd

←

$FF

None

1

BRANCH INSTRUCTIONS

RJMP

k

Relative Jump

PC

←

PC + k + 1

None

2

RCALL

k

Relative Subroutine Call

PC

←

PC + k + 1

None

3

RET

Subroutine Return

PC

←

STACK

None

4

RETI

Interrupt Return

PC

←

STACK

I

4

CPSE

Rd, Rr

Compare, Skip if Equal

if (Rd = Rr) PC

←

PC + 2 or 3

None

1/2

CP

Rd, Rr

Compare

Rd - Rr

Z,N,V,C,H

1

CPC

Rd, Rr

Compare with Carry

Rd - Rr - C

Z,N,V,C,H

1

CPI

Rd, K

Compare Register with Immediate

Rd - K

Z,N,V,C,H

1

SBRC

Rr, b

Skip if Bit in Register Cleared

if (Rr(b) = 0) PC

←

PC + 2 or 3

None

1/2

SBRS

Rr, b

Skip if Bit in Register is Set

if (Rr(b) = 1) PC

←

PC + 2 or 3

None

1/2

SBIC

P, b

Skip if Bit in I/O Register Cleared

if (P(b)= 0) PC

←

PC + 2 or 3

None

1/2

SBIS

P, b

Skip if Bit in I/O Register is Set

if (P(b) = 1) PC

←

PC + 2 or 3

None

1/2

BRBS

s, k

Branch if Status Flag Set

if (SREG(s) = 1) then PC

←

PC + k + 1

None

1/2

BRBC

s, k

Branch if Status Flag Cleared

if (SREG(s) = 0) then PC

←

PC + k + 1

None

1/2

BREQ

k

Branch if Equal

if (Z = 1) then PC

←

PC + k + 1

None

1/2

BRNE

k

Branch if Not Equal

if (Z = 0) then PC

←

PC + k + 1

None

1/2

BRCS

k

Branch if Carry Set

if (C = 1) then PC

←

PC + k + 1

None

1/2

BRCC

k

Branch if Carry Cleared

if (C = 0) then PC

←

PC + k + 1

None

1/2

BRSH

k

Branch if Same or Higher

if (C = 0) then PC

←

PC + k + 1

None

1/2

BRLO

k

Branch if Lower

if (C = 1) then PC

←

PC + k + 1

None

1/2

BRMI

k

Branch if Minus

if (N = 1) then PC

←

PC + k + 1

None

1/2

BRPL

k

Branch if Plus

if (N = 0) then PC

←

PC + k + 1

None

1/2

BRGE

k

Branch if Greater or Equal, Signed

if (N

⊕

V = 0) then PC

←

PC + k + 1

None

1/2

BRLT

k

Branch if Less than Zero, Signed

if (N

⊕

V = 1) then PC

←

PC + k + 1

None

1/2

BRHS

k

Branch if Half-carry Flag Set

if (H = 1) then PC

←

PC + k + 1

None

1/2

BRHC

k

Branch if Half-carry Flag Cleared

if (H = 0) then PC

←

PC + k + 1

None

1/2

BRTS

k

Branch if T-Flag Set

if (T = 1) then PC

←

PC + k + 1

None

1/2

BRTC

k

Branch if T-Flag Cleared

if (T = 0) then PC

←

PC + k + 1

None

1/2

BRVS

k

Branch if Overflow Flag is Set

if (V = 1) then PC

←

PC + k + 1

None

1/2

BRVC

k

Branch if Overflow Flag is Cleared

if (V = 0) then PC

←

PC + k + 1

None

1/2

BRIE

k

Branch if Interrupt Enabled

if (I = 1) then PC

←

PC + k + 1

None

1/2

BRID

k

Branch if Interrupt Disabled

if (I = 0) then PC

←

PC + k + 1

None

1/2

DATA TRANSFER INSTRUCTIONS

LD

Rd, Z

Load Register Indirect

Rd

←

(Z)

None

2

ST

Z, Rr

Store Register Indirect

(Z)

←

Rr

None

2

MOV

Rd, Rr

Move between Registers

Rd

←

Rr

None

1

LDI

Rd, K

Load Immediate

Rd

←

K

None

1

IN

Rd, P

In Port

Rd

←

P

None

1

OUT

P, Rr

Out Port

P

←

Rr

None

1