Rainbow Electronics MAX9860 User Manual

Page 21

MAX9860

16-Bit Mono Audio Voice Codec

______________________________________________________________________________________

21

LEFT

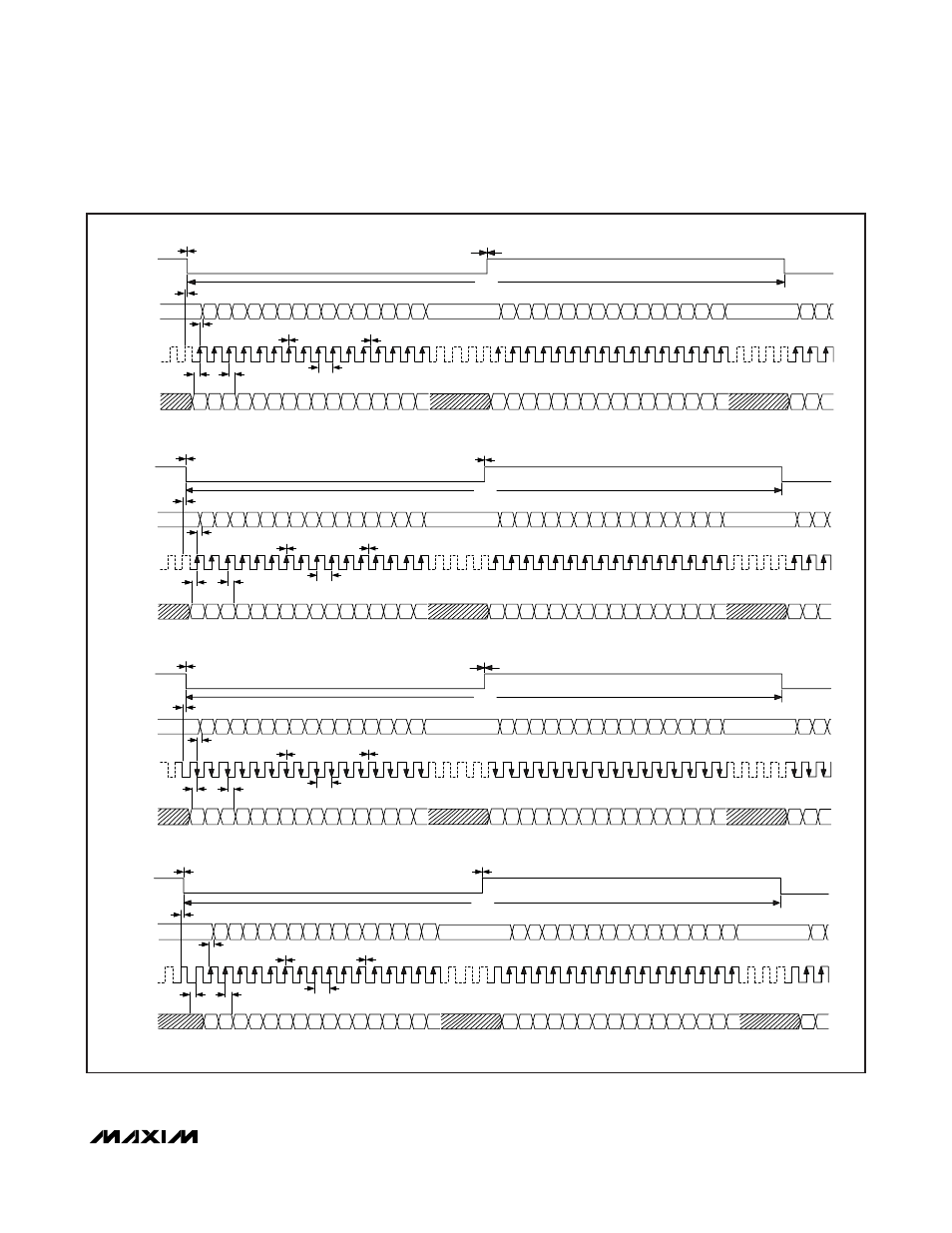

LEFT JUSTIFIED : WCI = 0, _BCI = 0, _DLY = 0

AUDIO MASTER MODES (ST = 1):

LEFT JUSTIFIED + LRCLK INVERT: WCI = 1, _BCI = 0, _DLY = 0

LEFT JUSTIFIED + BCLK INVERT: WCI = 0, _BCI = 1, _DLY = 0

I

2

S: WCI = 0, _BCI = 0, _DLY = 1

LRCLK

BCLK

SDOUT

SDIN

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

1/fS

CONFIGURED BY BSEL

7ns (typ)

7ns (typ)

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D15

D15

25ns (min)

7ns (typ)

7ns (typ)

0ns (min)

40ns (max)

0ns (min)

RELATIVE TO PCLK (NOTE 7)

RIGHT

RIGHT

LRCLK

BCLK

SDOUT

SDIN

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3

D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

1/f

S

CONFIGURED BY BSEL

7ns (typ)

7ns (typ)

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D15

D15

25ns (min)

7ns (typ)

7ns (typ)

0ns (min)

40ns (max)

0ns (min)

RELATIVE TO PCLK (NOTE 7)

LEFT

LEFT

LRCLK

BCLK

SDOUT

SDIN

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

1/fS

CONFIGURED BY BSEL

7ns (typ)

7ns (typ)

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D15

D15

25ns (min)

7ns (typ)

7ns (typ)

0ns (min)

40ns (max)

0ns (min)

RELATIVE TO PCLK (NOTE 7)

RIGHT

LEFT

LRCLK

BCLK

SDOUT

SDIN

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

1/fS

CONFIGURED BY BSEL

7ns (typ)

7ns (typ)

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D15

D15

25ns (min)

7ns (typ)

7ns (typ)

0ns (min)

40ns (max)

0ns (min)

RELATIVE TO PCLK (NOTE 7)

RIGHT

D0

D15

D15

D15

D15

D15

D15

D15

NOTE 7: THE DELAY FROM A BCLK EDGE AND AN LRCLK EDGE IS DETERMINED BY LENGTH OF TIME THAT PCLK (THE INTERNALLY DIVIDED DOWN VERSION OF MCLK AS DEFINED BY THE PSCLK BITS) IS HIGH DURING

ONE PERIOD OF MCLK PLUS THE INTERNAL DELAY. FOR EXAMPLE: IF PCLK = 12.288MHz, THE DELAY BETWEEN BCLK AND LRCLK IS TYPICALLY 45ns.

D15

D0

Figure 1. Digital Audio Interface Audio Master Mode Examples