Table 3. clock control registers (continued), Table 4. common n values – Rainbow Electronics MAX9860 User Manual

Page 18

MAX9860

16-Bit Mono Audio Voice Codec

18

______________________________________________________________________________________

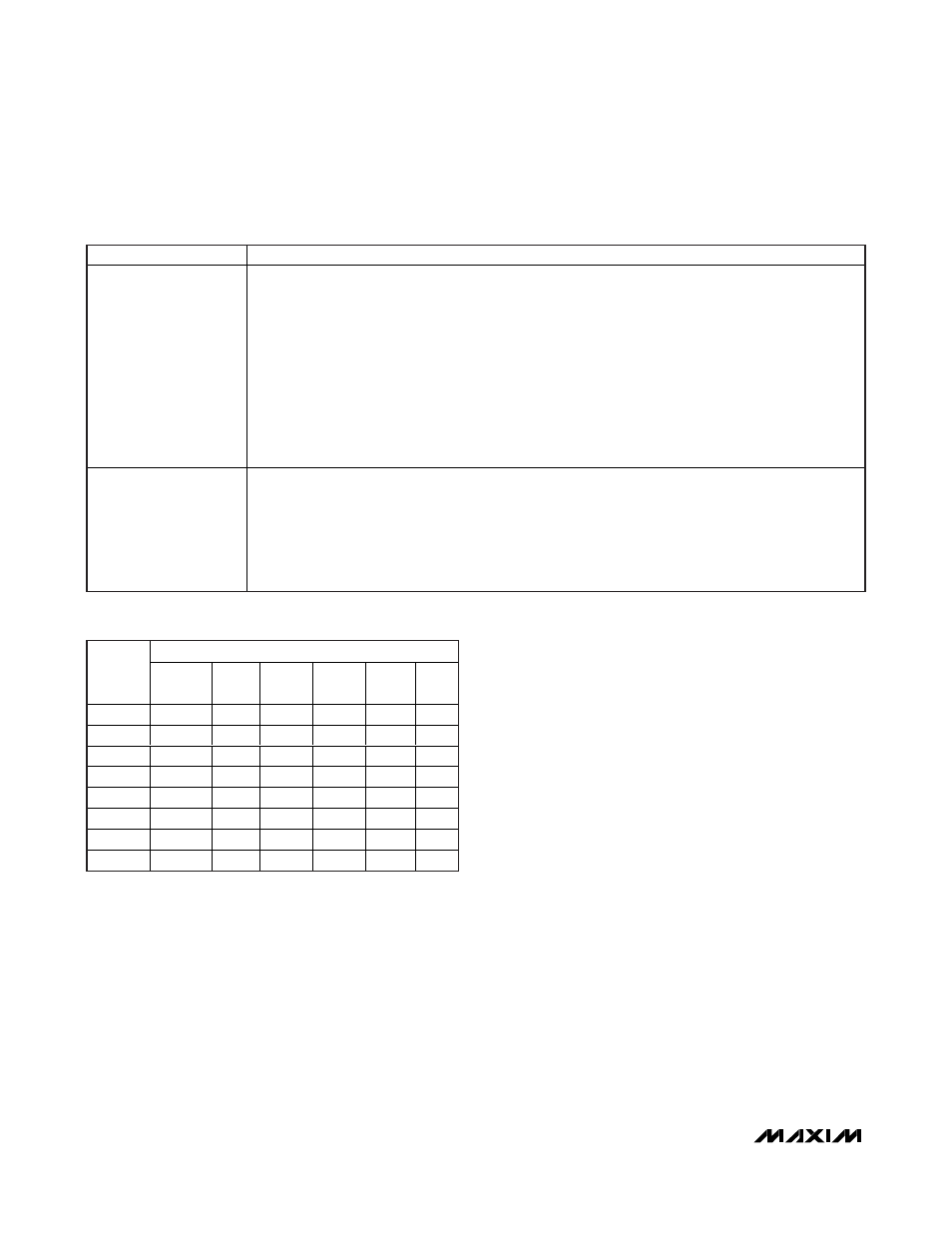

Table 3. Clock Control Registers (continued)

BITS

FUNCTION

PLL

PLL Enable

0 = (Valid for slave and master mode)—The frequency of LRCLK is set by the NHI and NLO divider

bits. Set PLL = 0 in slave mode only if the externally generated LRCLK can be exactly selected

using the LRCLK divider.

1 = (Valid for slave mode only)—Used when the audio master generates an LRCLK not selectable

using the LRCLK divider. A digital PLL locks on to the externally supplied LRCLK signal

regardless of the MCLK frequency.

Rapid Lock Mode

To enable rapid lock mode set NHI and NLO to the nearest desired ratio and set NLO[0] = 1 (Register

0x05, bit 0) before setting the PLL mode bit.

NHI and NLO

LRCLK Divider

NHI and NLO control a 15-bit clock divider (N). When the PLL = 0 and FREQ = 00, the frequency of

LRCLK is determined by the clock divider. See Table 4 for common N values.

N = (65,536 x 96 x f

LRCLK

)/f

PCLK

f

LRCLK

= LRCLK frequency

f

PCLK

= prescaled MCLK internal clock frequency (PCLK)

LRCLK (kHz)

MCLK

(MHz)

PSCLK

8

16

32

44.1

48

11.2896

01

116A

22D4

45A9

6000

687D

12

01

1062

20C5

4189

5A51

624E

12.288

01

1000

2000

4000

5833

6000

13

01

F20

1E3F

3C7F

535F

5ABE

19.2

01

A3D

147B

28F6

3873

3D71

24

10

1062

20C5

4189

5A51

624E

26

10

F20

1E3F

3C7F

535F

5ABE

27

10

E90

1D21

3A41

5048

5762

Table 4. Common N Values

Note: Values in bold italics are exact integers that provide

maximum full-scale performance.