Table 3. clock control registers – Rainbow Electronics MAX9860 User Manual

Page 17

Clock Control

The MAX9860 can work with a master clock (MCLK)

supplied from any system clock within the range of

10MHz to 60MHz. Internally, the MAX9860 requires a

10MHz to 20MHz clock so a prescaler divides by 1, 2,

or 4 to create the internal clock (PCLK). PCLK is used

to clock all portions of the MAX9860.

The MAX9860 is capable of supporting any sample rate

from 8kHz to 48kHz, including all common sample rates

(8kHz, 16kHz, 24kHz, 32kHz, 44.1kHz, 48kHz). To

accommodate a wide range of system architectures,

the MAX9860 supports three main clocking modes:

Normal Mode: This mode uses a 15-bit clock divider

coefficient to set the sample rate relative to the

prescaled MCLK input (PCLK). This allows high flexibili-

ty in both the MCLK and LRCLK frequencies and can

be used in either master or slave mode.

Exact Integer Mode: Common MCLK frequencies

(12MHz, 13MHz, and 19.2MHz) can be programmed to

operate in exact integer mode for both 8kHz and 16kHz

sample rates. In these modes, the MCLK and LRCLK

rates are selected by using the FREQ and 16KHZ bits

instead of the NHI, NLO, and PLL control bits.

PLL Mode: When operating in slave mode, a PLL can

be enabled to lock onto externally generated LRCLK

signals that are asynchronously related to PCLK.

MAX9860

16-Bit Mono Audio Voice Codec

______________________________________________________________________________________

17

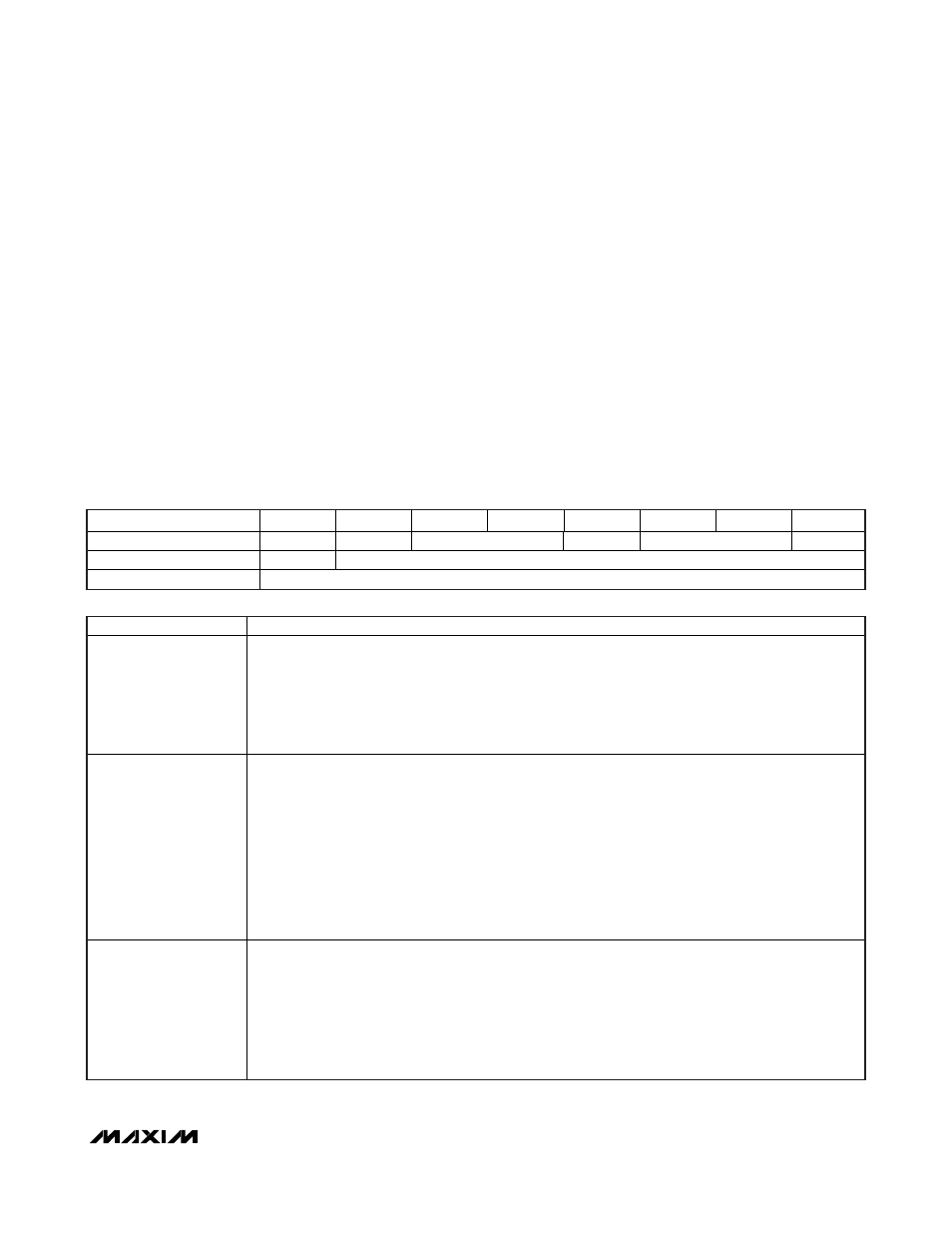

Table 3. Clock Control Registers

REGISTER ADDRESS

B7

B6

B5

B4

B3

B2

B1

B0

0x03

0

0

PSCLK

0

FREQ

16KHZ

0x04

PLL

NHI

0x05

NLO

BITS

FUNCTION

PSCLK[1:0]

MCLK Prescaler

Divides MCLK down to generate a PCLK between 10MHz and 20MHz.

00 = Disable clock for low-power shutdown.

01 = Select if MCLK is between 10MHz and 20MHz.

10 = Select if MCLK is between 20MHz and 40MHz.

11 = Select if MCLK is greater than 40MHz.

FREQ[1:0]

Integer Clock Mode

Enables exact integer mode for three predefined PCLK frequencies. Exact integer mode is normally

intended for master mode, but can be enabled in slave mode if the externally supplied LRCLK exactly

matches the frequency specified in each mode.

00 = Normal operation (configure clocking with the PLL, NHI, and NLO bits).

01 = Select when PCLK is 12MHz (LRCLK = PCLK/1500 or PCLK/750).

10 = Select when PCLK is 13MHz (LRCLK = PCLK/1625 or PCLK/812.5).

11 = Select when PCLK is 19.2MHz (LRCLK = PCLK/2400 or PCLK/1200).

When FREQ

≠ 00, the PLL, NHI, and NLO bits are unused.

16KHZ

16kHz Mode

When FREQ

≠ 00:

0 = LRCLK is exactly 8kHz.

1 = LRCLK is exactly 16kHz.

When FREQ = 00, 16KHZ is used to set the AGC clock rate:

0 = Use when LRCLK

≤ 24kHz.

1 = Use when LRCLK > 24kHz.