Table 5. digital audio interface registers – Rainbow Electronics MAX9860 User Manual

Page 19

Digital Audio Interface

The MAX9860’s digital audio interface supports a wide

range of operating modes to ensure maximum compati-

bility. See Figures 1 through 4 for timing diagrams. In

master mode, the MAX9860 outputs LRCLK and BCLK,

while in slave mode, they are inputs. When operating in

master mode, BCLK can be configured in a number of

ways to ensure compatiblity with other audio devices.

MAX9860

16-Bit Mono Audio Voice Codec

______________________________________________________________________________________

19

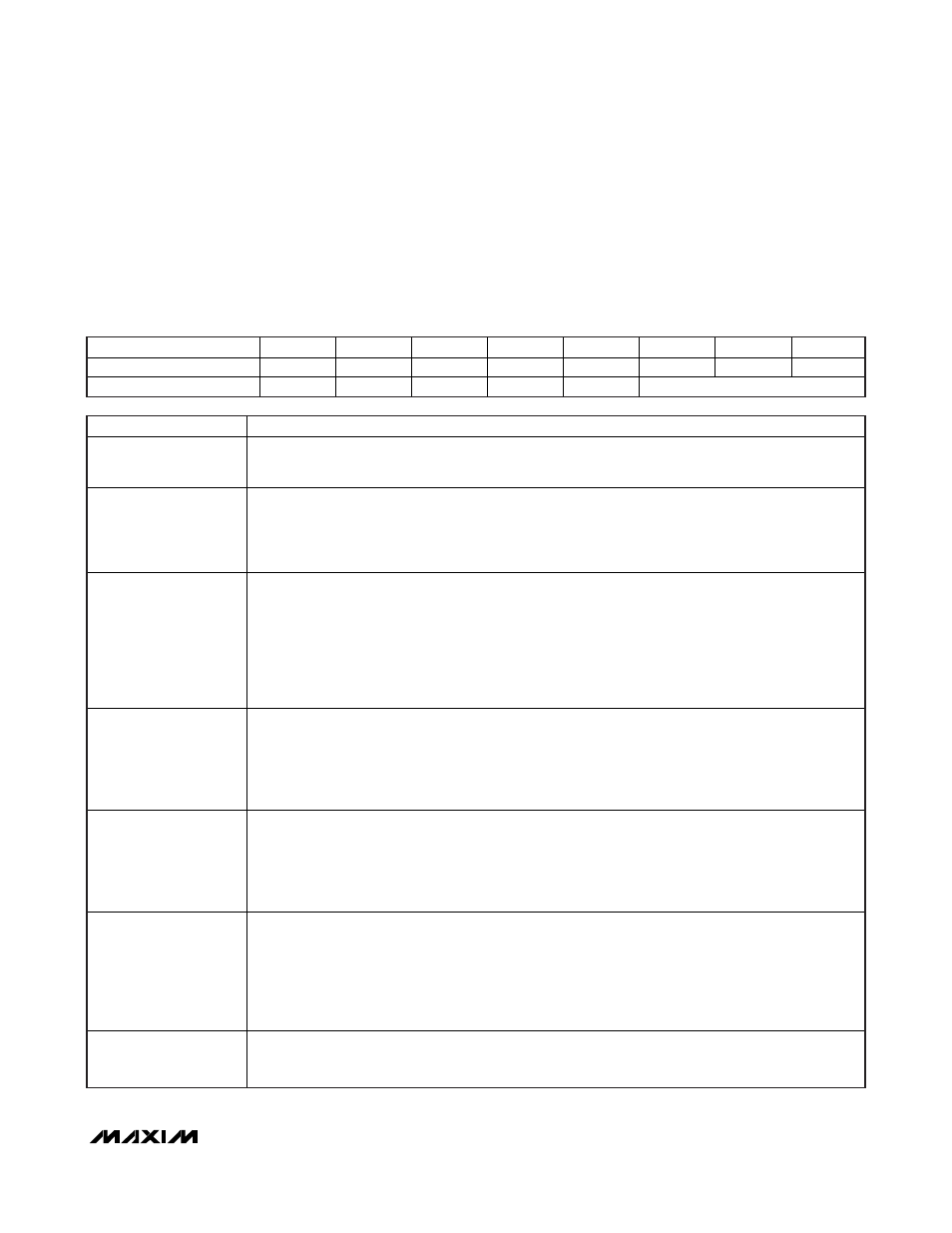

Table 5. Digital Audio Interface Registers

REGISTER ADDRESS

B7

B6

B5

B4

B3

B2

B1

B0

0x06

MAS

WCI

DBCI

DDLY

HIZ

TDM

0

0

0x07

0

0

ABCI

ADLY

ST

BSEL

BITS

FUNCTION

MAS

Master Mode

0 = The MAX9860 operates in slave mode with LRCLK and BCLK configured as inputs.

1 = The MAX9860 operates in master mode with LRCLK and BCLK configured as outputs.

WCI

LRCLK Invert

0 = Left-channel data is input and output while LRCLK is low.

1 = Right-channel data is input and output while LRCLK is low.

WCI is ignored when TDM = 1.

DBCI

DAC BCLK Invert (must be set to ABCI)

In master and slave mode:

0 = SDIN is latched into the part on the rising edge of BCLK.

1 = SDIN is latched into the part on the falling edge of BCLK.

In master mode:

0 = LRCLK changes state following the rising edge of BCLK.

1 = LRCLK changes state following the falling edge of BCLK.

DDLY

DAC Delay Mode

0 = SDIN data is latched on the first BCLK edge following an LRCLK edge.

1 = SDIN data is assumed to be delayed one BCLK cycle so that it is latched on the 2nd BCLK edge

following an LRCLK edge (I

2

S-compatible mode).

DDLY is ignored when TDM = 1.

HIZ

SDOUT High-Impedance Mode

0 = SDOUT is set either high or low after all data bits have been transferred out of the part.

1 = SDOUT goes to a high-impedance state after all data bits have been transferred out of the part,

allowing SDOUT to be shared by other devices.

Use HIZ only when TDM = 1.

TDM

TDM Mode Select

0 = LRCLK signal polarity indicates left and right audio.

1 = LRCLK is a framing pulse which transitions polarity to indicate the start of a frame of audio data

consisting of multiple channels.

W hen op er ati ng i n TD M m od e the l eft channel i s outp ut i m m ed i atel y fol l ow i ng the fr am e sync p ul se. If r i g ht-

channel d ata i s b ei ng tr ansm i tted , the 2nd channel of d ata i m m ed i atel y fol l ow s the 1st channel d ata.

ABCI

ADC BCLK Invert (must be set to DBCI)

0 = SDOUT is valid on the rising edge of BCLK and transitions immediately after the rising edge.

1 = SDOUT is valid on the falling edge of BCLK and transitions immediately after the falling edge.