Max6964, Output led driver/gpo with intensity control, Table 2. register address map – Rainbow Electronics MAX6964 User Manual

Page 8

MAX6964

during the high period of the clock pulse. When the

master is transmitting to the MAX6964, the device gen-

erates the acknowledge bit because the MAX6964 is

the recipient. When the MAX6964 is transmitting to the

master, the master generates the acknowledge bit

because the master is the recipient.

Slave Address

The MAX6964 has a 7-bit long slave address (

Figure 6

).

The eighth bit following the 7-bit slave address is the

R/W bit. The R/W bit is low for a write command, high

for a read command.

The second (A5), third (A4), fourth (A3), sixth (A1), and

last (A0) bits of the MAX6964 slave address are always

1, 0, 0, 0, and 0. Slave address bits A6 and A2 are

selected by the address input AD0. AD0 can be con-

nected to GND, V+, SDA, or SCL. The MAX6964 has

four possible slave addresses (

Table 1

), and therefore

a maximum of four MAX6964 devices can be controlled

independently from the same interface.

Message Format for Writing the MAX6964

A write to the MAX6964 comprises the transmission of

the MAX6964’s slave address with the R/W bit set to

zero, followed by at least 1 byte of information. The first

byte of information is the command byte. The command

byte determines which register of the MAX6964 is to be

written to by the next byte, if received (

Table 2

). If a

STOP condition is detected after the command byte is

received, then the MAX6964 takes no further action

beyond storing the command byte.

Any bytes received after the command byte are data

bytes. The first data byte goes into the internal register of

the MAX6964 selected by the command byte (

Figure 8

).

17-Output LED Driver/GPO

with Intensity Control

8

_______________________________________________________________________________________

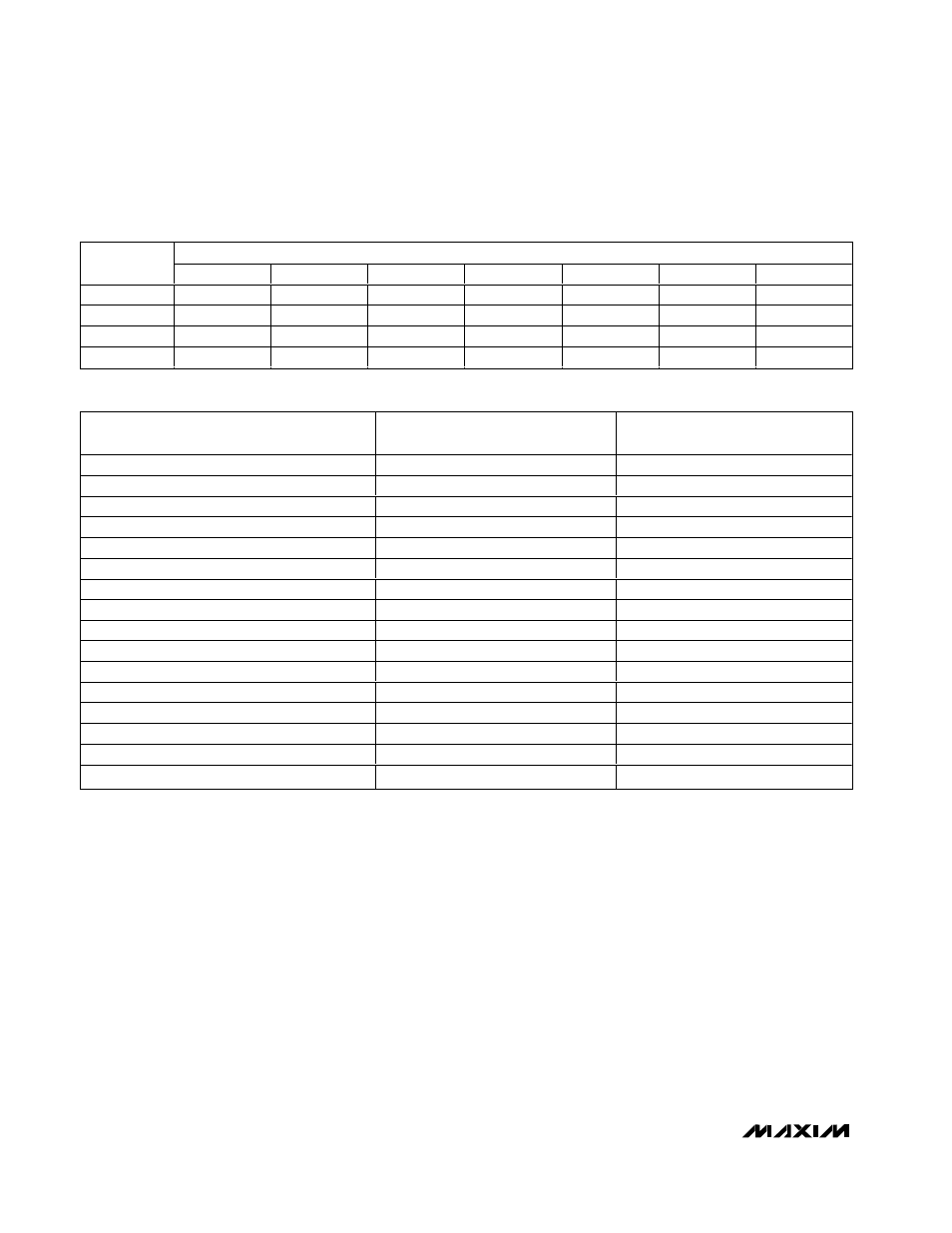

Table 1. MAX6964 Address Map

DEVICE ADDRESS

PIN AD0

A6

A5

A4

A3

A2

A1

A0

SCL

1

1

0

0

0

0

0

SDA

1

1

0

0

1

0

0

GND

0

1

0

0

0

0

0

V+

0

1

0

0

1

0

0

Table 2. Register Address Map

REGISTER

ADDRESS CODE

(hex)

AUTOINCREMENT

ADDRESS

Blink phase 0 outputs O7–O0

0x02

0x03

Blink phase 0 outputs O15–O8

0x03

0x02

User RAM0

0x06

0x07

User RAM1

0x07

0x06

Blink phase 1 outputs O7–O0

0x0A

0x0B

Blink phase 1 outputs O15–O8

0x0B

0x0A

Master and global/O16 intensity

0x0E

—

Configuration

0x0F

—

Outputs intensity O1, O0

0x10

0x11

Outputs intensity O3, O2

0x11

0x12

Outputs intensity O5, O4

0x12

0x13

Outputs intensity O7, O6

0x13

0x14

Outputs intensity O9, O8

0x14

0x15

Outputs intensity O11, O10

0x15

0x16

Outputs intensity O13, O12

0x16

0x17

Outputs intensity O15, O14

0x17

0x10