C interface specification – Rainbow Electronics MAX9877 User Manual

Page 24

MAX9877

Low RF Susceptibility, Mono Audio

Subsystem with DirectDrive Headphone Amplifier

24

______________________________________________________________________________________

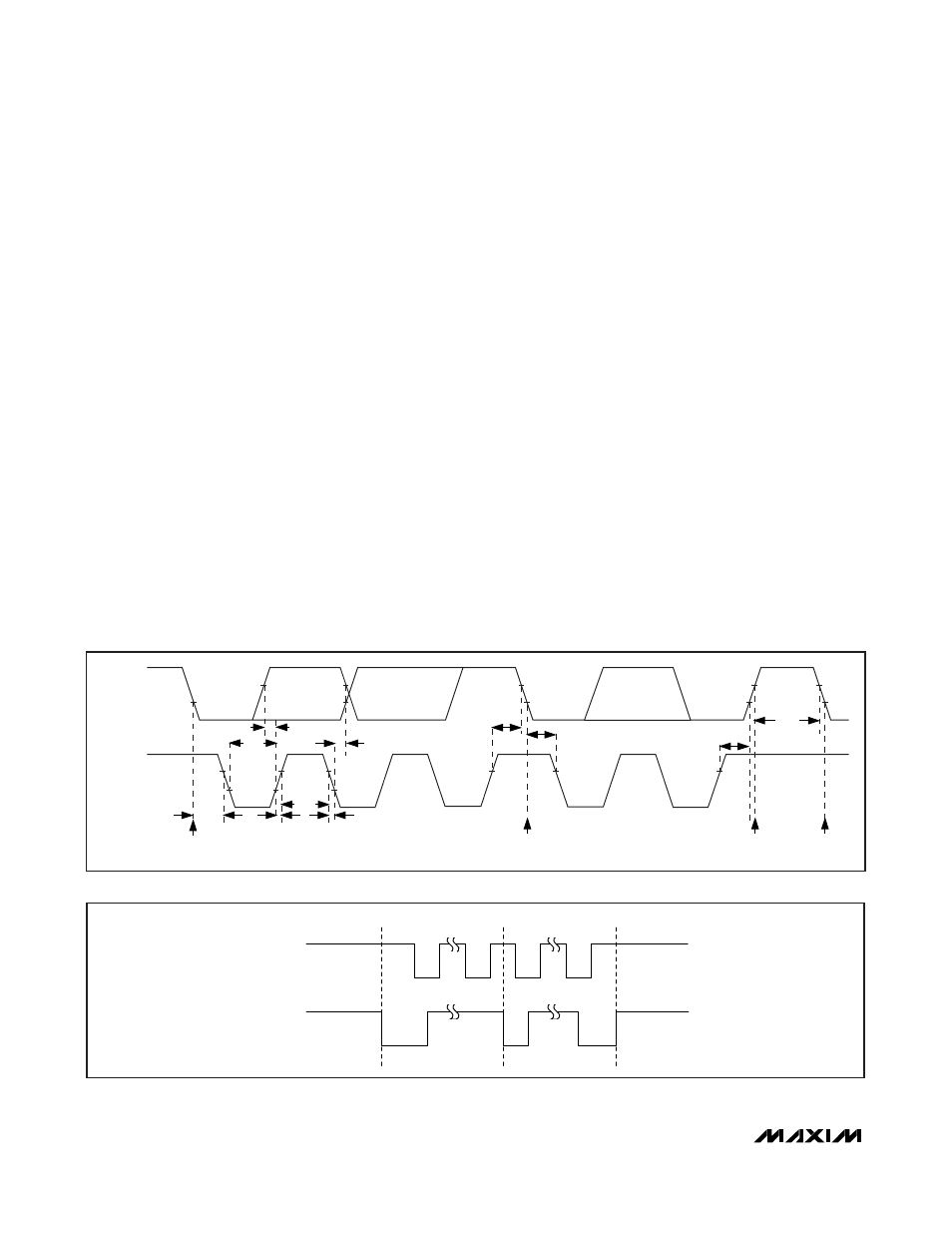

SCL

SDA

START

CONDITION

STOP

CONDITION

REPEATED

START CONDITION

START

CONDITION

t

HD:STA

t

SU:STA

t

SU:STA

t

BUF

t

SU:STO

t

LOW

t

SU:DAT

t

HD:DAT

t

HIGH

t

R

t

F

Figure 6. 2-Wire Interface Timing Diagram

SCL

SDA

S

Sr

P

Figure 7. START, STOP, and REPEATED START Conditions

SMBus is a trademark of Intel Corp.

I

2

C Interface Specification

The MAX9877 features an I

2

C/SMBus™-compatible, 2-

wire serial interface consisting of a serial-data line

(SDA) and a serial-clock line (SCL). SDA and SCL facil-

itate communication between the MAX9877 and the

master at clock rates up to 400kHz. Figure 6 shows the

2-wire interface timing diagram. The master generates

SCL and initiates data transfer on the bus. The master

device writes data to the MAX9877 by transmitting the

proper slave address followed by the register address

and then the data word. Each transmit sequence is

framed by a START (S) or REPEATED START (Sr) con-

dition and a STOP (P) condition. Each word transmitted

to the MAX9877 is 8 bits long and is followed by an

acknowledge clock pulse. A master reading data from

the MAX9877 transmits the proper slave address fol-

lowed by a series of nine SCL pulses. The MAX9877

transmits data on SDA in sync with the master-generat-

ed SCL pulses. The master acknowledges receipt of

each byte of data. Each read sequence is framed by a

START (S) or REPEATED START (Sr) condition, a not

acknowledge, and a STOP (P) condition. SDA operates

as both an input and an open-drain output. A pullup

resistor, typically greater than 500

Ω, is required on

SDA. SCL operates only as an input. A pullup resistor,

typically greater than 500

Ω, is required on SCL if there

are multiple masters on the bus, or if the single master

has an open-drain SCL output. Series resistors in line

with SDA and SCL are optional. Series resistors protect

the digital inputs of the MAX9877 from high voltage

spikes on the bus lines, and minimize crosstalk and

undershoot of the bus signals.

Bit Transfer

One data bit is transferred during each SCL cycle. The

data on SDA must remain stable during the high period

of the SCL pulse. Changes in SDA while SCL is high

are control signals (see the

START and STOP

Conditions

section).

START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A

master initiates communication by issuing a START con-

dition. A START condition is a high-to-low transition on

SDA with SCL high. A STOP condition is a low-to-high

transition on SDA while SCL is high (Figure 7). A START

condition from the master signals the beginning of a

transmission to the MAX9877. The master terminates

transmission, and frees the bus, by issuing a STOP con-

dition. The bus remains active if a REPEATED START

condition is generated instead of a STOP condition.