definition of terms, Definition of terms – Rainbow Electronics T89C51RD2 User Manual

Page 66

Rev. F - 15 February, 2001

66

T89C51RD2

Note 1: P3.2 is pulled low during programming to indicate RDY/BUSY.

(P3.2 = 1 Ready; P3.2 = 0 Busy).

Note 2: In Page Load Mode the current byte is loaded on ALE rising edge.

Note 3: After a power up all external test mode to program or to erase the FLASH are locked to avoid any untimely programming or erasure.

After each programming or erasure test mode, it’s advised to lock this feature (test mode PELCK).

To validate the test mode mode PEULCK the following sequence has to be applied:

Test Mode PEULCK with ALE = 1.

Pulse on ALE (min width=25clk) with P0=55 (P0 latched on ALE rising edge)

Pulse on ALE (min width=25clk) with P0=AA (P0 latched on ALE rising edge)

Note 4: The highest security bit (bit 7) is used to secure the 7 lowest bit erasure. The only way to erase this bit is to erase the whole FLASH

memory.

Procedure to program security bits (After array programming):

- program bit7 to 0, program all other bits ( 1 = erased, 0 = programmed).

- test mode PGMS (din = HSB).

Procedure to erase security byte:

- test mode CERR: erase all array included HSB.

- program hardware security byte to FF: test mode PGMS (din = FF).

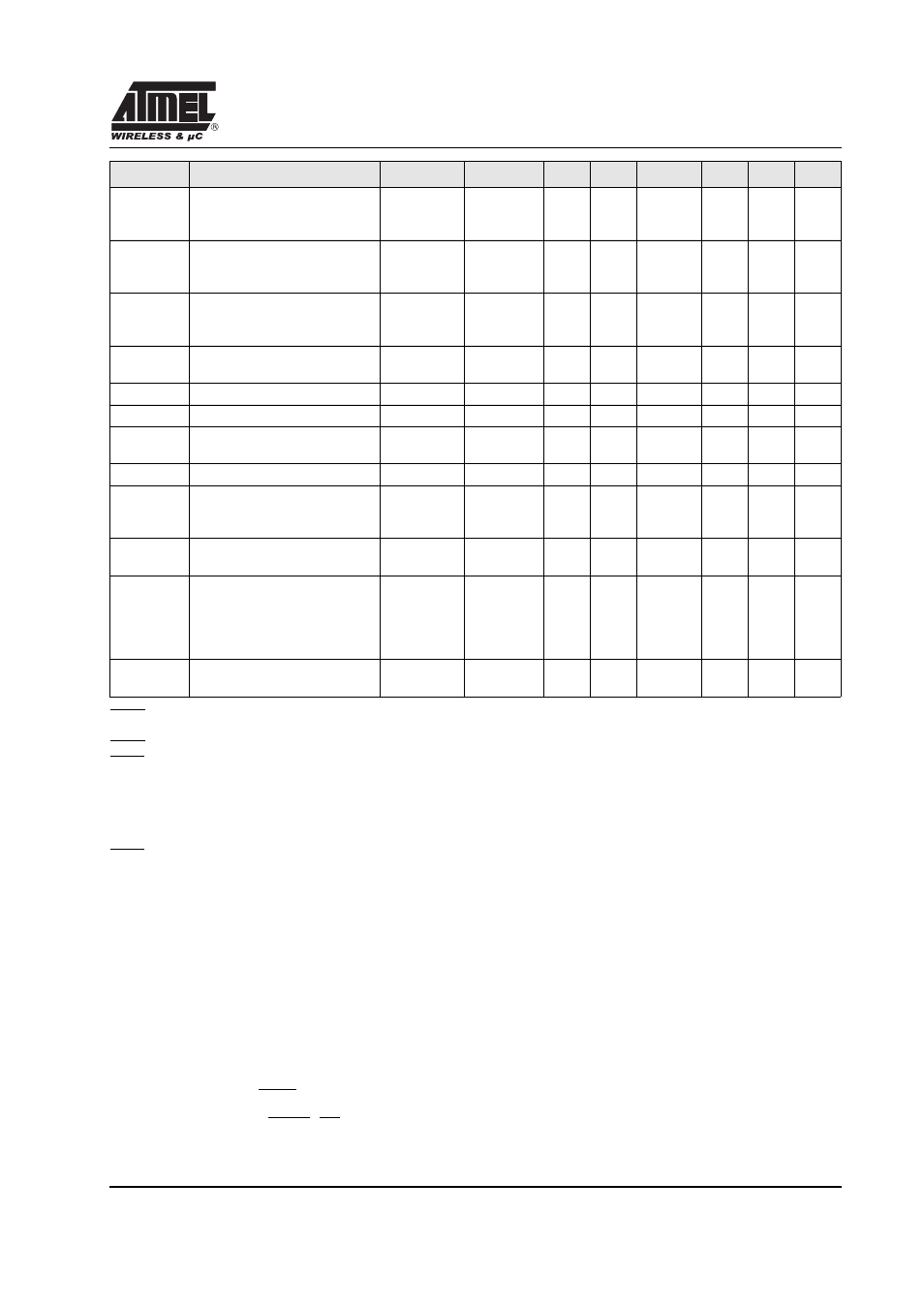

8.9.3. Definition of terms

Address Lines:P1.0-P1.7, P2.0-P2.5, P3.4-P3.5, respectively for A0-A15.

Data Lines:P0.0-P0.7 for D0-D7

Control Signals:RST, PSEN, P2.6, P2.7, P3.2, P3.3, P3.6, P3.7.

Program Signals: ALE/PROG, EA

Mode Name

Mode

P1[7..0]

P2[5..0]

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

PELCK

Program or Erase Lock.

Disable the Erasure or Programming

access

xx

xx

x

x

x

1

x

x

PEULCK

Program or Erase UnLock.

Enable the Erasure or Programming

access

xx

xx

x

x

x

0

x

x

PGMC

Write Code Data (byte)

or write Page

Always precedeed by PGML

A7-A0

A13-A8

1

x

Note1

0

A14

A15

PGML

Memory Page Load

(up to 128 bytes)

A7-A0

A13-A8

1

x

x

0

A14

A15

PGMV

Read Code Data (byte)

A7-A0

A13-A8

1

x

x

1

A14

A15

VSB

Read Security Byte (=HSB)

xx

xx

1

x

x

1

x

x

PGMS

Write lock Byte (Note 4)

(security byte = HSB)

xx

xx

1

x

Note1

0

x

x

CERR

Chip Erase User + XAF

xx

xx

1

x

x

0

x

x

PGXC

Write Byte or Page Extra Memory

(XAF)

Always precedeed by PGXL

A7-A0

(0-7F)

xx

1

x

Note1

0

x

x

PGXL

Memory Page Load XAF

(up to 128 bytes)

A7-A0

(0-7F)

xx

1

x

x

1

x

x

TMS

Read Signature bytes

30h (Manufacturer code)

31h (Device ID #1)

60h (Device ID #2)

61h (Device ID #3)

30h

31h

60h

61h

x

x

x

x

1

x

x

RXAF

Read Extra Memory

(XAF)

Addr

(0-7F)

00

1

x

x

0

x

x