Rainbow Electronics T89C51RD2 User Manual

Page 11

11

Rev. F - 15 February, 2001

T89C51RD2

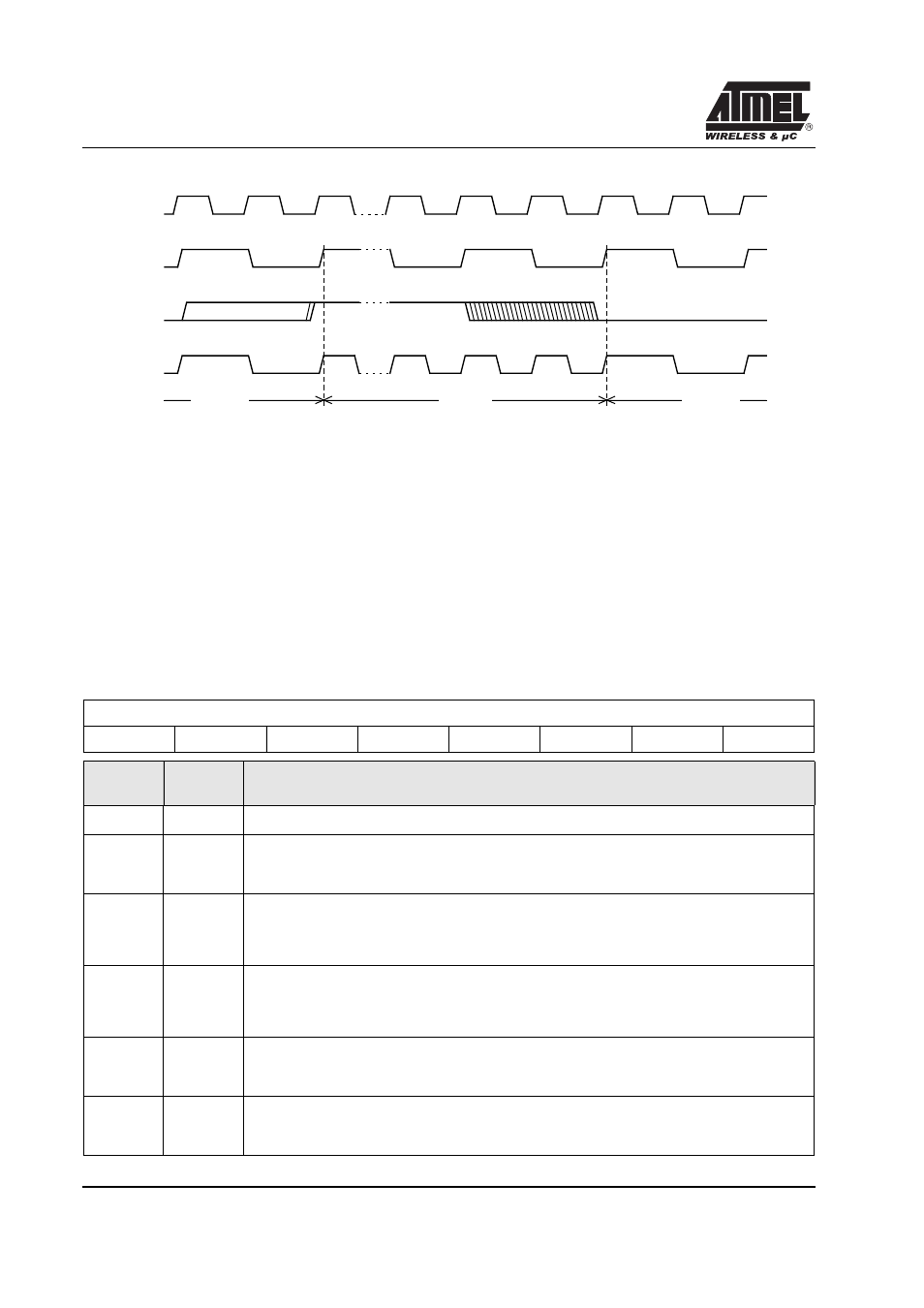

Figure 2. Mode Switching Waveforms

The X2 bit in the CKCON register (See Table 2.) allows to switch from 12 clock periods per instruction to 6

clock periods and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the

X2 feature (X2 mode).

The T0X2, T1X2, T2X2, SiX2, PcaX2 and WdX2 bits in the CKCON register (See Table 2.) allow to switch from

standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods

per peripheral clock cycle). These bits are active only in X2 mode.

More information about the X2 mode can be found in the application note ANM072 "How to take advantage of

the X2 features in TS80C51 microcontroller?"

Table 2. CKCON Register

CKCON - Clock Control Register (8Fh)

7

6

5

4

3

2

1

0

-

WdX2

PcaX2

SiX2

T2X2

T1X2

T0X2

X2

Bit

Number

Bit

Mnemonic

Description

7

-

Reserved

6

WdX2

Watchdog clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

5

PcaX2

Programmable Counter Array clock (This control bit is validated when the CPU clock X2 is set; when X2 is

low, this bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

4

SiX2

Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2

is low, this bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

3

T2X2

Timer2 clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

2

T1X2

Timer1 clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle

XTAL1:2

XTAL1

CPU clock

X2 bit

X2 Mode

STD Mode

STD Mode