pca watchdog timer – Rainbow Electronics T89C51RD2 User Manual

Page 31

31

Rev. F - 15 February, 2001

T89C51RD2

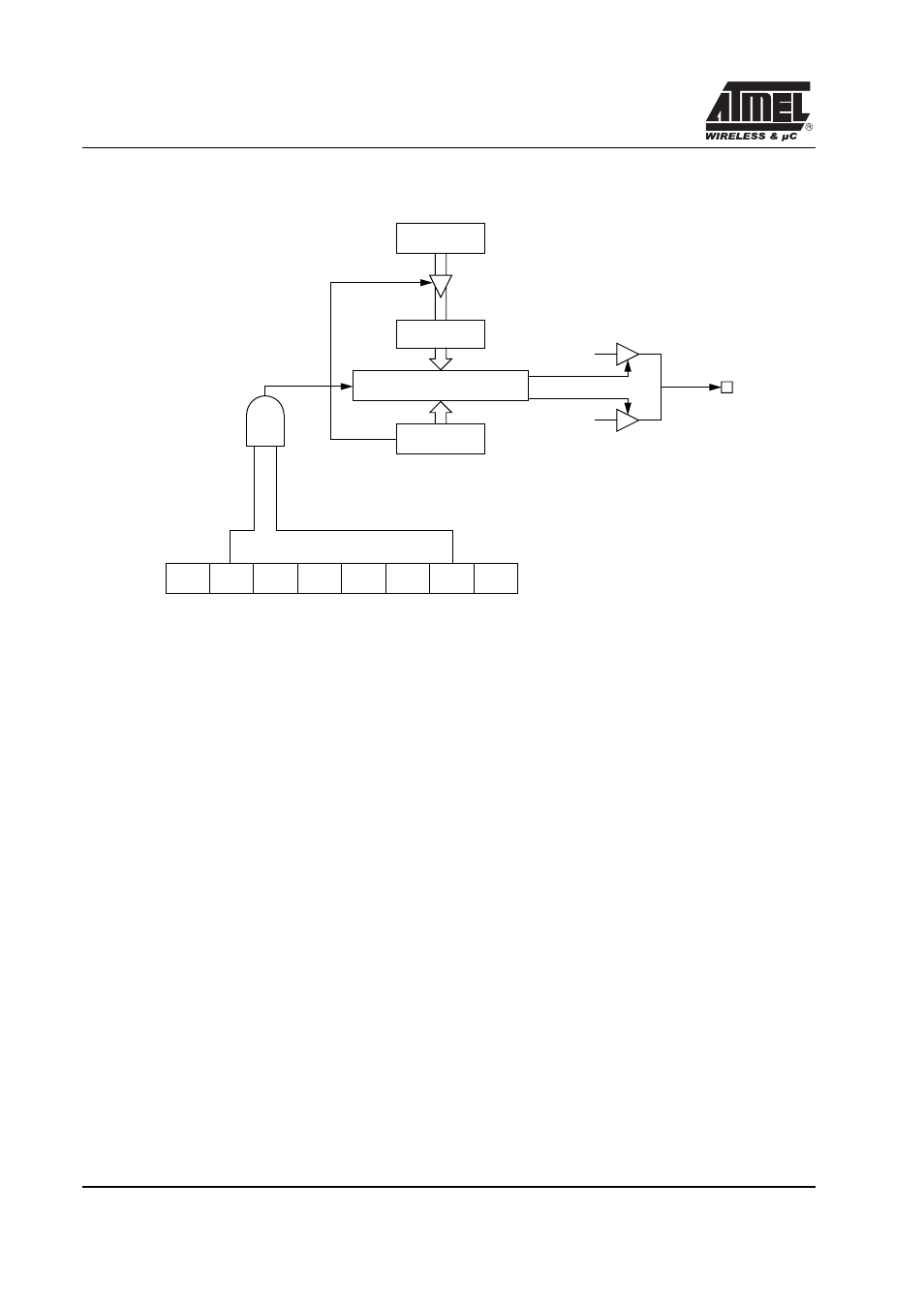

SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from

FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The

PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Figure 12. PCA PWM Mode

6.5.5. PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing

chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic

discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can

still be used for other modes if the watchdog is not needed. Figure 10 shows a diagram of how the watchdog

works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit

value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This

will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

•

1. periodically change the compare value so it will never match the PCA timer,

•

2. periodically change the PCA timer value so it will never match the compare values, or

•

3. disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program

counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not

recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules;

changing the time base for other modules would not be a good idea. Thus, in most applications the first solution

is the best option.

This watchdog timer won’t generate a reset out on the reset pin.

CL

CCAPnH

CCAPnL

ECOMn

CCAPMn, n= 0 to 4

0xDA to 0xDE

CAPNn MATn

TOGn PWMn ECCFn

CAPPn

8 bit comparator

CEXn

“0”

“1”

≥

<

Enable

PCA counter/timer

Overflow