Rainbow Electronics T89C51RD2 User Manual

Page 23

23

Rev. F - 15 February, 2001

T89C51RD2

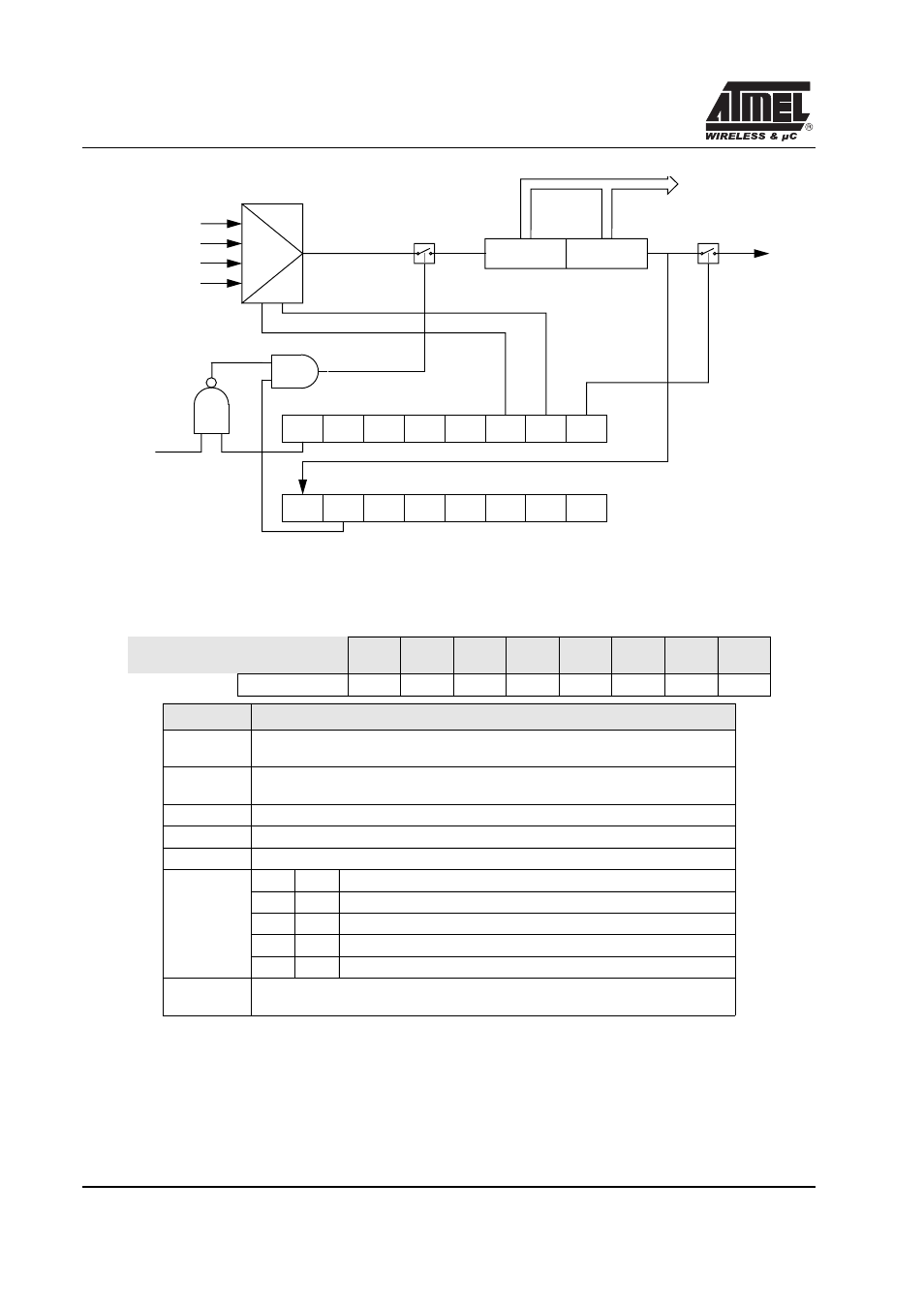

Figure 7. PCA Timer/Counter

Table 7. CMOD: PCA Counter Mode Register

The CMOD SFR includes three additional bits associated with the PCA (See Figure 7 and Table 7).

•

The CIDL bit which allows the PCA to stop during idle mode.

•

The WDTE bit which enables or disables the watchdog function on module 4.

CMOD

Address 0D9H

CIDL

WDTE

-

-

-

CPS1

CPS0

ECF

Reset value

0

0

X

X

X

0

0

0

Symbol

Function

CIDL

Counter Idle control: CIDL = 0 programs the PCA Counter to continue functioning during

idle Mode. CIDL = 1 programs it to be gated off during idle.

WDTE

Watchdog Timer Enable: WDTE = 0 disables Watchdog Timer function on PCA Module 4.

WDTE = 1 enables it.

-

Not implemented, reserved for future use.

a

a.

User software should not write 1s to reserved bits. These bits may be used in future 8051 family

products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its

active value will be 1. The value read from a reserved bit is indeterminate.

CPS1

PCA Count Pulse Select bit 1.

CPS0

PCA Count Pulse Select bit 0.

CPS1

CPS0

Selected PCA input.

b

b.

f

osc

= oscillator frequency

0

0

Internal clock f

osc

/12 ( Or f

osc

/6 in X2 Mode).

0

1

Internal clock f

osc

/4 ( Or f

osc

/2 in X2 Mode).

1

0

Timer 0 Overflow

1

1

External clock at ECI/P1.2 pin (max rate = f

osc

/ 8)

ECF

PCA Enable Counter Overflow interrupt: ECF = 1 enables CF bit in CCON to generate an

interrupt. ECF = 0 disables that function of CF.

CIDL

CPS1

CPS0

ECF

It

CH

CL

16 bit up/down counter

To PCA

modules

Fosc /12

Fosc / 4

T0 OVF

P1.2

Idle

CMOD

0xD9

WDTE

CF

CR

CCON

0xD8

CCF4

CCF3

CCF2

CCF1

CCF0

overflow