9 self-refresh mode, 10 reset considerations, Diagram – Texas Instruments TMS320C6452 DSP User Manual

Page 26: 9 self-refresh mode 2.10 reset considerations

www.ti.com

2.9

Self-Refresh Mode

2.10 Reset Considerations

Hard

reset from

PLLCTL1

DDR

PSC

DDR2

memory

controller

registers

State

machine

VRST

VCTL_RST

Peripheral Architecture

Setting the self refresh (SR) bit in the SDRAM refresh control register (SDRFC) to 1 forces the DDR2

memory controller to place the external DDR2 SDRAM in a low-power mode (self refresh), in which the

DDR2 SDRAM maintains valid data while consuming a minimal amount of power. When the SR bit is

asserted, the DDR2 memory controller continues normal operation until all outstanding memory access

requests have been serviced and the refresh backlog has been cleared. At this point, all open pages of

DDR2 SDRAM are closed and a self-refresh (SLFRFR) command (an autorefresh command with

DDR_CKE low) is issued.

The DDR2 memory controller exits the self-refresh state when a memory access is received or when the

SR bit in SDRFC is cleared. While in the self-refresh state, if a request for a memory access is received,

the DDR2 memory controller services the memory access request, returning to the self-refresh state upon

completion.

The DDR2 memory controller will not exit the self-refresh state (whether from a memory access request or

from clearing the SR bit) until T_CKE + 1 cycles have expired since the self-refresh command was issued.

The value of T_CKE is defined in the SDRAM timing 2 register (SDTIM2).

After exiting from the self-refresh state, the DDR2 memory controller will not immediately start using

commands. Instead, it will wait T_SXNR + 1 clock cycles before issuing non-read commands and

T_SXRD + 1 clock cycles before issuing read commands. The SDRAM timing 2 register (SDTIM2)

programs the values of T_SXNR and T_SXRD.

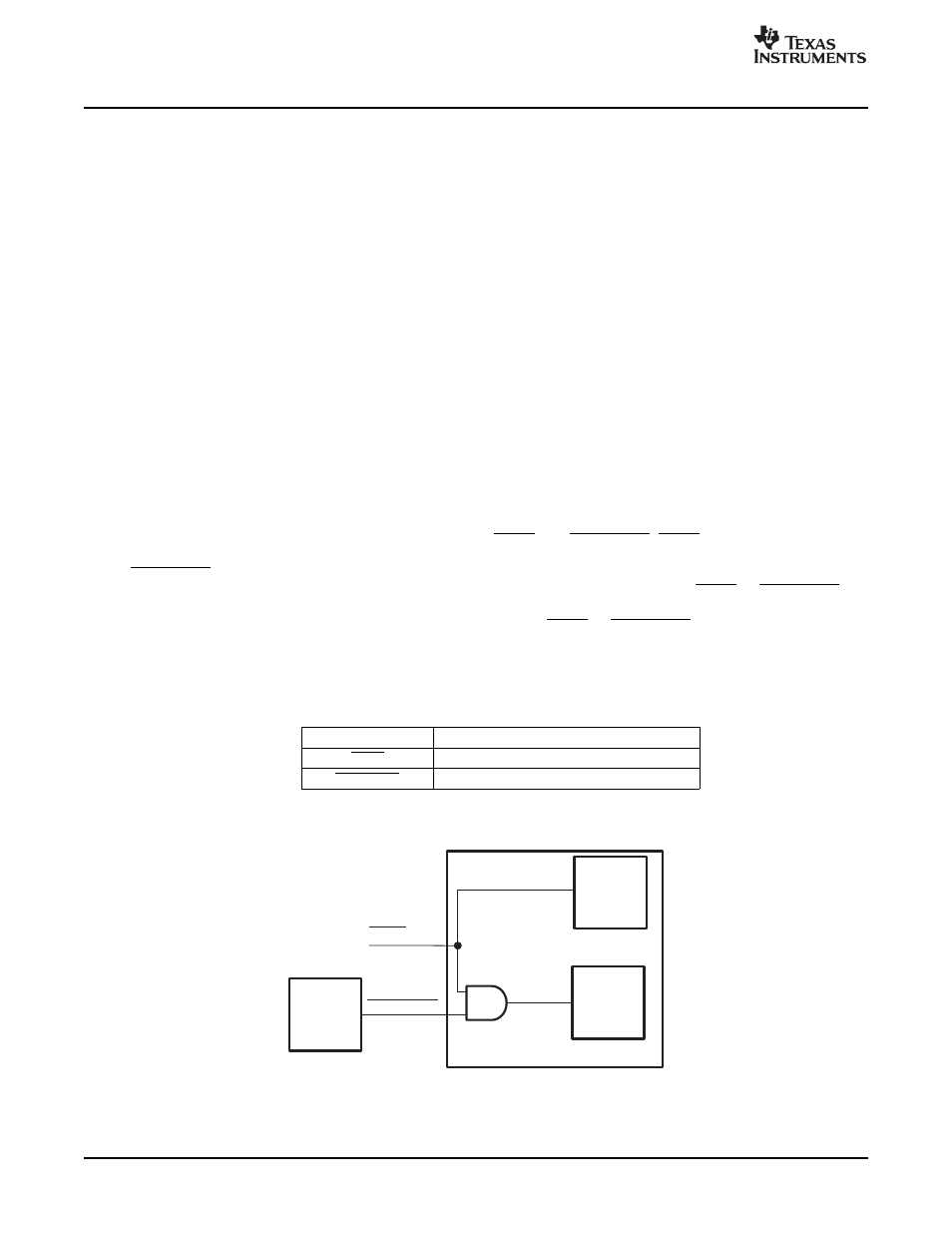

The DDR2 memory controller has two reset signals, VRST and VCTL_RST. VRST is a module-level reset

that resets both the state machine and the DDR2 memory controller memory-mapped registers.

VCTL_RST resets the state machine only. If the DDR2 memory controller is reset independently of other

peripherals, your software should not perform memory or register accesses while VRST or VCTL_RST are

asserted. If memory or register accesses are performed while the DDR2 memory controller is in the reset

state, other masters may hang. Following the rising edge of VRST or VCTL_RST, the DDR2 memory

controller FIFOs are lost.

describes the different methods for asserting each reset signal. The

Power and Sleep Controller (PSC) acts as a master controller for power management for all of the

peripherals on the device.

Table 8. Reset Sources

Reset Signal

Reset Source

VRST

Hardware/device reset

VCTL_RST

Power and sleep controller

Figure 16. DDR2 Memory Controller Reset Block Diagram

DSP DDR2 Memory Controller

26

SPRUF85 – October 2007