4 deactivation (dcab and deac), Command – Texas Instruments TMS320C6452 DSP User Manual

Page 16

www.ti.com

2.4.4

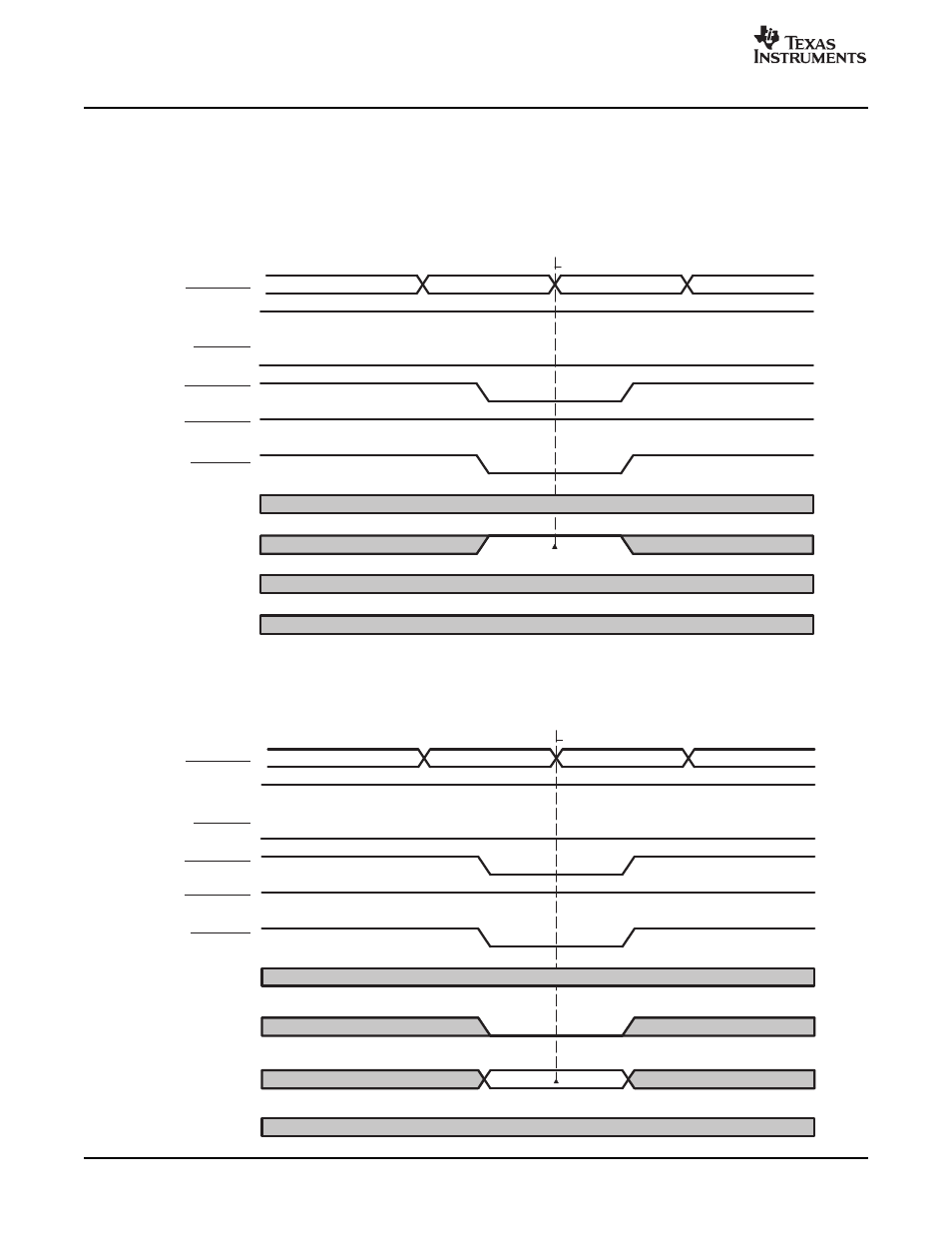

Deactivation (DCAB and DEAC)

DCAB

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_A[13:11, 9:0]

DDR_A[10]

DEAC

DDR_CLK

DDR_CLK

DDR_CS

DDR_CKE

DDR_RAS

DDR_WE

DDR_DQM[3:0]

DDR_CAS

DDR_BA[2:0]

DDR_A[13:11, 9:0]

DDR_A[10]

Peripheral Architecture

The precharge all banks command (DCAB) is performed after a reset to the DDR2 memory controller or

following the initialization sequence. DDR2 SDRAMs also require this cycle prior to a refresh (REFR) and

mode set register commands (MRS and EMRS). During a DCAB command, DDR_A[10] is driven high to

ensure the deactivation of all banks.

shows the timing diagram for a DCAB command.

Figure 6. DCAB Command

The DEAC command closes a single bank of memory specified by the bank select signals.

shows

the timings diagram for a DEAC command.

Figure 7. DEAC Command

DSP DDR2 Memory Controller

16

SPRUF85 – October 2007

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)