Texas Instruments TCM4300 User Manual

Page 49

4–14

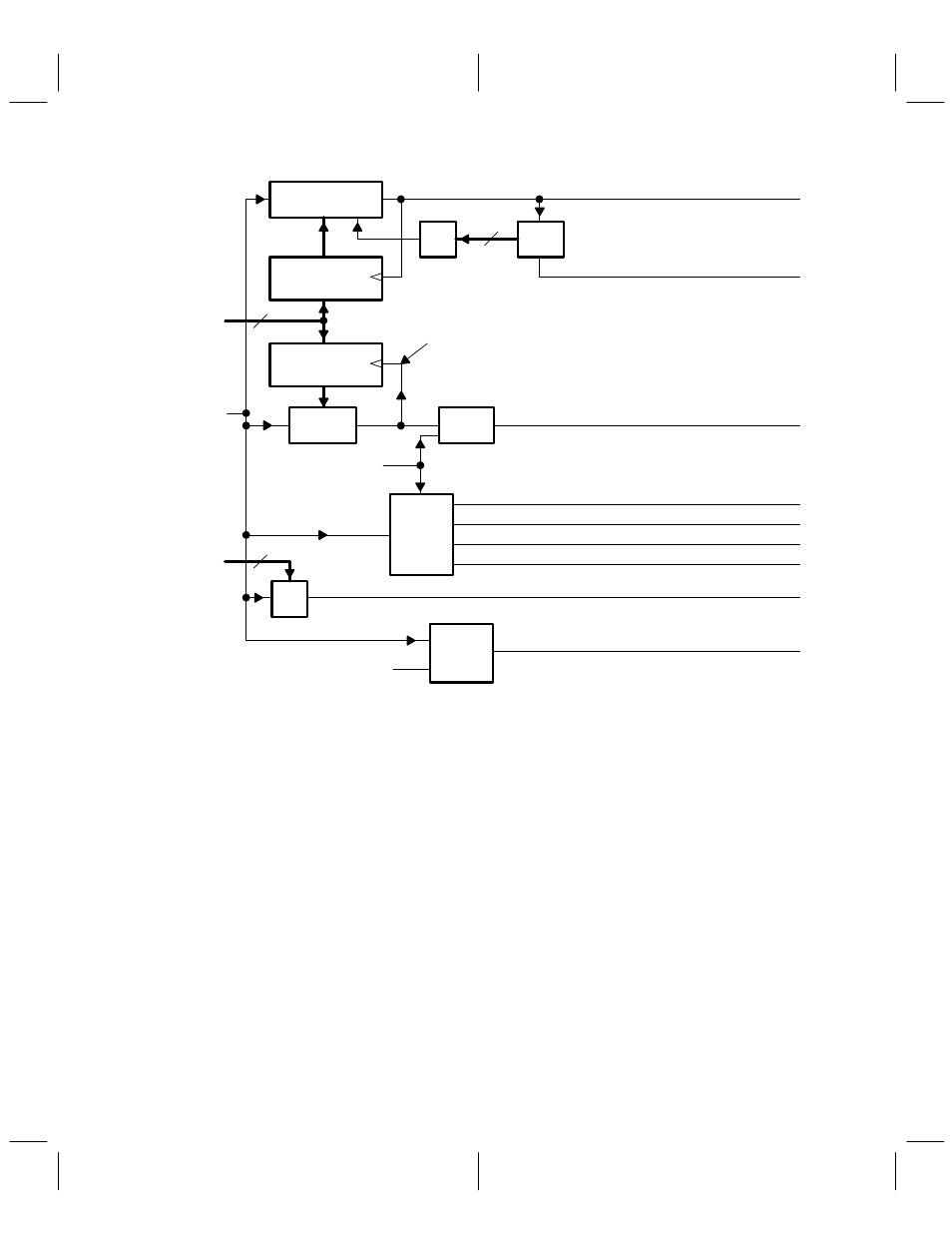

÷

17, 18, 19, 20

Adjust

Counter B

= 0

÷

256

Bits 0 – 5

RCO

Adjust

Counter A

÷

3, 4, 5

Phase-Adjusted

9.72-MHz Clock

ч

243/

ч

200

Clock

Divider

Chain

Analog/Digital

Mode (MODE bit)

Frequency Synth. Clock 303.75 kHz

WBD Demod. 6.48 MHz

ADC Clocks

DAC Clocks

÷

N

5

10

N = (2, 3, . . . 32)

Sync.

Enable

Logic

MCLKEN

From

Micro-

controller

38.88 MHz

MCLKIN

From DSP

Microcontroller Clock MCCLK

External Clock Output MCLKOUT

Analog/Digital

40.0/48.6-kHz A/ D Sample Clock (SINT)

8-kHz Codec Sample Clock CSCLK

2.048-MHz Codec Master Clock CMCLK

Figure 4–5. Timing and Clock Generation for 38.88-MHz Clock