Philips SC28L91 User Manual

Page 34

Philips Semiconductors

Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

34

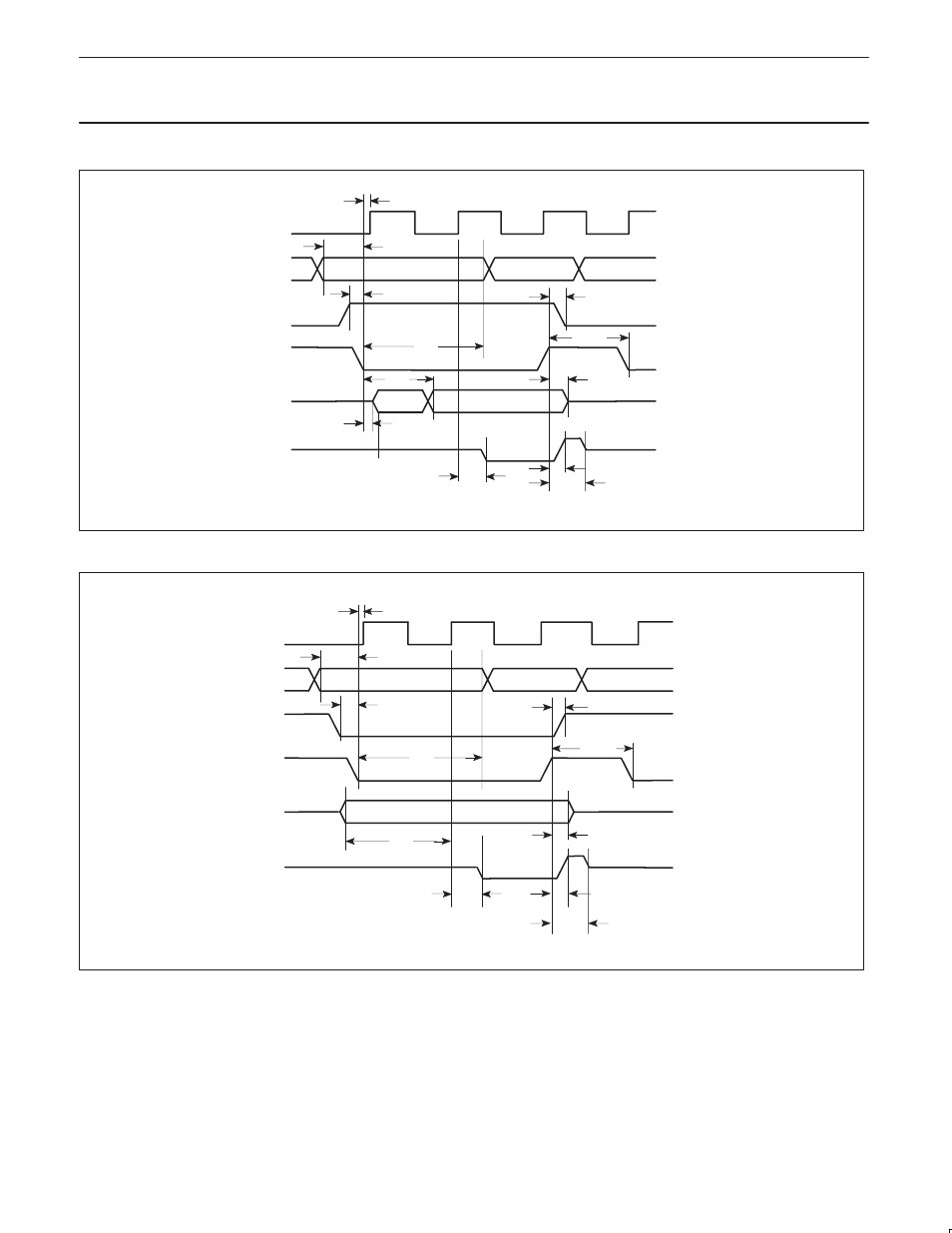

X1/CLK

A1–A4

RWN

CSN

D0–D7

DTACKN

t

CSC

t

AS

t

CS

t

DF

t

DAT

t

DAH

t

CH

t

RWD

t

DD

t

DCR

t

AH

DATA VALID

NOT

VALID

t

DA

NOTE: DACKN low requires two rising edges of X1 clock after CSN is low.

SD00687

Figure 6. Bus Timing (Read Cycle) (68XXX mode)

X1/CLK

A1–A4

RWN

CSN

D0–D7

DTACKN

t

CSC

t

AS

t

CS

t

DH

t

DAT

t

DAH

t

CH

t

RWD

t

DS

t

DCW

t

AH

NOTE: DACKN low requires two rising edges of X1 clock after CSN is low.

SD00688

Figure 7. Bus Timing (Write Cycle) (68XXX mode)

NOTE:

For Figures 6 and 7 WRN changing within the time of CEN low may cause short read or write pulses that could upset internal pointers and

registers. Bus action terminates on the rise of CEN or the fall of DACKN, which ever occurs first.

- AZ382 (14 pages)

- AZ 7272 (25 pages)

- AZ1006CD (15 pages)

- CD 482 (10 pages)

- ACT500/01 (2 pages)

- AZ7794 (2 pages)

- AX3218 (14 pages)

- AZ102IN (2 pages)

- AZ9203/11 (62 pages)

- AZ1015 (2 pages)

- 170C5 (89 pages)

- AX1000/11AX1000/11 (17 pages)

- AZ 6805 (20 pages)

- AZ 7465 (22 pages)

- AZ 6188 (21 pages)

- AQ 5040 (5 pages)

- AZ 7183 (26 pages)

- MAGNAVOX AZ1518 (22 pages)

- AZ5140/98 (2 pages)

- AX2401 (2 pages)

- AZ 6897 (12 pages)

- CDR880BK (2 pages)

- CDR880BK (19 pages)

- AZ 7566 (20 pages)

- AX 5100/01 (9 pages)

- AX5319 (13 pages)

- AJ100 (2 pages)

- AJ100 (17 pages)

- AZ 8040 (15 pages)

- AK 691 (14 pages)

- AX5122 (10 pages)

- CDI200/37 (24 pages)

- CD 750 (18 pages)

- AZ 1565/00 (63 pages)

- AZ 7482/00 (20 pages)

- CD 624 (14 pages)

- AX5200 (2 pages)

- AZ 8214 (14 pages)

- AX3311 (6 pages)

- AZ 7474 (20 pages)

- AZ5150 (20 pages)

- CDI740/05 (20 pages)

- AK 640 (16 pages)

- CD163/05 (12 pages)

- AZ102H (14 pages)