Philips SC28L91 User Manual

Page 29

Philips Semiconductors

Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

29

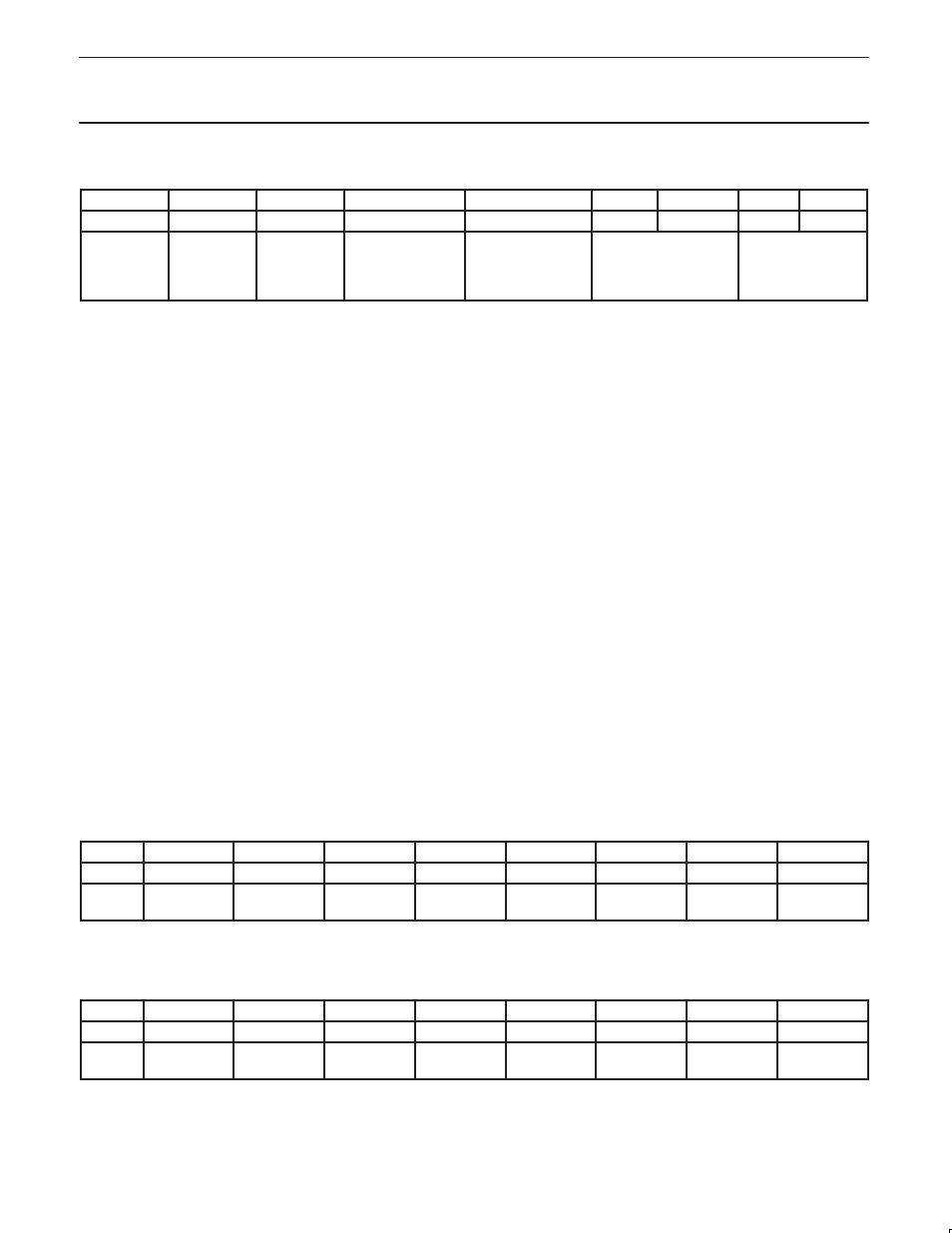

OPCR Output Port Configuration Register

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

OPCR

OP7

OP6

OP5

OP4

OP3

OP2

OP1

OP0

0x0D

0 = OPR[7]

0 = OPR[6]

0 = OPR[5]

0 = OPR[4]

00 = OPR[3]

00 = OPR[2]

1 = Reserved

1 = TxRDY

1 = Reserved

1 = RxRDY/FFULL

01 = C/T OUTPUT

01 = TxC(16X)

10 = Reserved

10 = TxC(1X)

11 = Reserved

11 = RxC(1X)

OPCR[7]—OP7 Output Select

This bit programs the OP7 output to provide one of the following:

0

The complement of OPR[7].

1

reserved

OPCR[6]—OP6 Output Select

This bit programs the OP6 output to provide one of the following:

0

The complement of OPR[6].

1

The transmitter interrupt output which is the complement of

ISR[0]. When in this mode OP6 acts as an open-drain out-

put. Note that this output is not masked by the contents of

the IMR.

OPCR[5]—OP5 Output Select

This bit programs the OP5 output to provide one of the following:

0

The complement of OPR[5].

1

Reserved

OPCR[4]—OP4 Output Select

This field programs the OP4 output to provide one of the following:

0

The complement of OPR[4].

1

The receiver interrupt output which is the complement of

ISR[1]. When in this mode OP4 acts as an open-drain out-

put. Note that this output is not masked by the contents of

the IMR.

OPCR[3:2]—OP3 Output Select

This bit programs the OP3 output to provide one of the following:

00

The complement of OPR[3].

01

The counter/timer output, in which case OP3 acts as an

open-drain output. In the timer mode, this output is a square

wave at the programmed frequency. In the counter mode,

the output remains High until terminal count is reached, at

which time it goes Low. The output returns to the High state

when the counter is stopped by a stop counter command.

Note that this output is not masked by the contents of the

IMR.

10

Reserved

11

Reserved

OPCR[1:0]—OP2 Output Select

This field programs the OP2 output to provide one of the following:

00

The complement of OPR[2].

01

The 16X clock for the transmitter. This is the clock selected

by CSR[3:0], and will be a 1X clock if CSR[3:0] = 1111.

10

The 1X clock for the transmitter, which is the clock that shifts

the transmitted data. If data is not being transmitted, a free

running 1X clock is output.

11

The 1X clock for the receiver, which is the clock that samples

the received data. If data is not being received, a free run-

ning 1X clock is output.

SOPR—Set the Output Port Bits (OPR)

SOPR[7:0]—Ones in the byte written to this register will cause the corresponding bit positions in the OPR to set to 1. Zeros have no effect. This

allows software to set individual bits with our keeping a copy of the OPR bit configuration.

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

SOPR

OP 7

OP 6

OP 5

OP 4

OP 3

OP 2

OP 1

OP 0

0x0E

1 = set bit

1 = set bit

1 = set bit

1 = set bit

1 = set bit

1 = set bit

1 = set bit

1 = set bit

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

ROPR—Reset Output Port Bits (OPR)

ROPR[7:0]—Ones in the byte written to the ROPR will cause the corresponding bit positions in the OPR to set to 0. Zeros have no effect. This

allows software to reset individual bits with our keeping a copy of the OPR bit configuration.

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ROPR

OP 7

OP 6

OP 5

OP 4

OP 3

OP 2

OP 1

OP 0

0x0F

1 = reset bit

1 = reset bit

1 = reset bit

1 = reset bit

1 = reset bit

1 = reset bit

1 = reset bit

1 = reset bit

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change

0 = no change