Philips SC28L91 User Manual

Page 14

Philips Semiconductors

Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

14

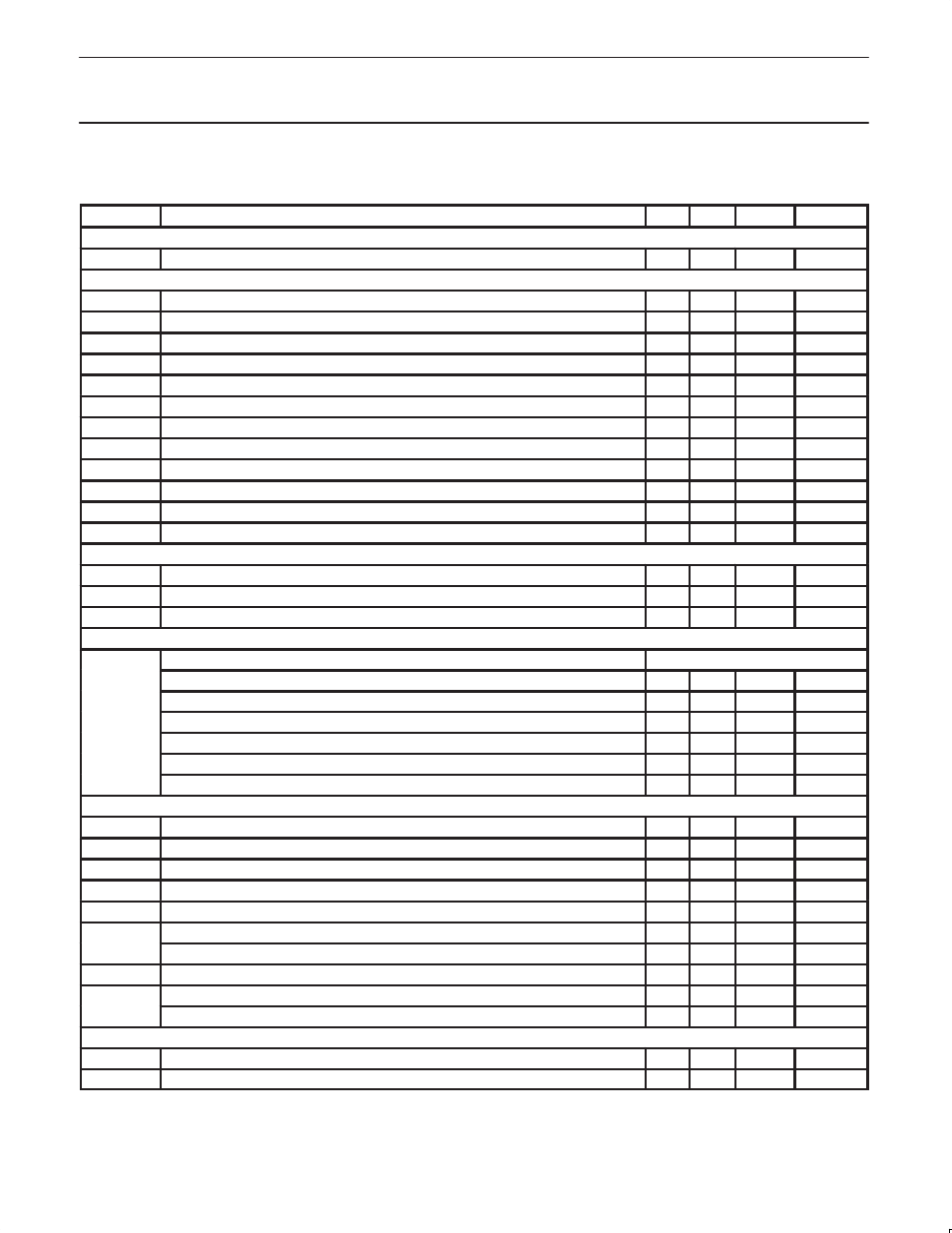

AC CHARACTERISTICS (3.3 VOLT)

1, 2, 3, 4

V

CC

= 3.3 V

±

10 %, T

amb

= –40

°

C to +85

°

C, unless otherwise specified.

ББББ

ББББ

Symbol

БББББББББББББББББББББ

БББББББББББББББББББББ

Parameter

БББ

БББ

Min

БББ

БББ

Typ

ББББ

ББББ

Max

ББББ

ББББ

Unit

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Reset Timing (See Figure 4)

ББББ

ББББ

t

RES

БББББББББББББББББББББ

БББББББББББББББББББББ

Reset pulse width

БББ

БББ

100

БББ

БББ

20

ББББ

ББББ

ББББ

ББББ

ns

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Bus Timing

5

(See Figure 5)

ББББ

t

*AS

БББББББББББББББББББББ

A0–A3 setup time to RDN, WRN Low

БББ

10

БББ

6

ББББ

ББББ

ns

ББББ

ББББ

t

*AH

БББББББББББББББББББББ

БББББББББББББББББББББ

A0–A3 hold time from RDN, WRN low

БББ

БББ

33

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*CS

БББББББББББББББББББББ

БББББББББББББББББББББ

CEN setup time to RDN, WRN low

БББ

БББ

0

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*CH

БББББББББББББББББББББ

БББББББББББББББББББББ

CEN Hold time from RDN. WRN low

БББ

БББ

0

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*RW

БББББББББББББББББББББ

БББББББББББББББББББББ

WRN, RDN pulse width (Low time)

БББ

БББ

20

БББ

БББ

10

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*DD

БББББББББББББББББББББ

БББББББББББББББББББББ

Data valid after RDN low (125pF load. See Figure 3 for smaller loads.)

БББ

БББ

БББ

БББ

46

ББББ

ББББ

75

ББББ

ББББ

ns

ББББ

ББББ

t

*DA

БББББББББББББББББББББ

БББББББББББББББББББББ

RDN low to data bus active

6

БББ

БББ

0

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*DF

БББББББББББББББББББББ

БББББББББББББББББББББ

Data bus floating after RDN or CEN high

БББ

БББ

БББ

БББ

15

ББББ

ББББ

20

ББББ

ББББ

ns

ББББ

ББББ

t

*DI

БББББББББББББББББББББ

БББББББББББББББББББББ

RDN or CEN high to data bus invalid

7

БББ

БББ

0

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББ

t

*DS

БББББББББББББББББББББ

Data bus setup time before WRN or CEN high (write cycle)

БББ

43

БББ

ББББ

ББББ

ns

ББББ

ББББ

t

*DH

БББББББББББББББББББББ

БББББББББББББББББББББ

Data hold time after WRN high

БББ

БББ

0

БББ

БББ

–15

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*RWD

БББББББББББББББББББББ

БББББББББББББББББББББ

High time between read and/or write cycles

5, 7

БББ

БББ

27

БББ

БББ

ББББ

ББББ

ББББ

ББББ

ns

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Port Timing

5

(See Figure 9)

ББББ

ББББ

t

*PS

БББББББББББББББББББББ

БББББББББББББББББББББ

Port in setup time before RDN low (Read IP ports cycle)

БББ

БББ

0

БББ

БББ

–20

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*PH

БББББББББББББББББББББ

БББББББББББББББББББББ

Port in hold time after RDN high

БББ

БББ

0

БББ

БББ

–20

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*PD

БББББББББББББББББББББ

БББББББББББББББББББББ

OP port valid after WRN or CEN high (OPR write cycle)

БББ

БББ

БББ

БББ

50

ББББ

ББББ

75

ББББ

ББББ

ns

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Interrupt Timing (See Figure 10)

ББББ

t

*IR

БББББББББББББББББББББ

INTRN (or OP3–OP7 when used as interrupts) negated from:

БББББББББББ

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Read RxFIFO (RxRDY/FFULL interrupt)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Write TxFIFO (TxRDY interrupt)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Reset Command (delta break change interrupt)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Stop C/T command (Counter/timer interrupt)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Read IPCR (delta input port change interrupt)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

Write IMR (Clear of change interrupt mask bit(s))

БББ

БББ

БББ

БББ

40

ББББ

ББББ

79

ББББ

ББББ

ns

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Clock Timing (See Figure 11)

ББББ

ББББ

t

*CLK

БББББББББББББББББББББ

БББББББББББББББББББББ

X1/CLK high or low time

БББ

БББ

35

БББ

БББ

25

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

f

*CLK

БББББББББББББББББББББ

БББББББББББББББББББББ

X1/CLK frequency

8

(for higher speeds contact factory)

БББ

БББ

0.1

БББ

БББ

3.686

ББББ

ББББ

8

ББББ

ББББ

MHz

ББББ

ББББ

f

*CTC

БББББББББББББББББББББ

БББББББББББББББББББББ

C/T Clk (IP2) high or low time (C/T external clock input)

БББ

БББ

30

БББ

БББ

15

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

f

*CTC

БББББББББББББББББББББ

БББББББББББББББББББББ

C/T Clk (IP2) frequency

8

(for higher speeds contact factory)

БББ

БББ

0

БББ

БББ

ББББ

ББББ

8

ББББ

ББББ

MHz

ББББ

ББББ

t

*RX

БББББББББББББББББББББ

БББББББББББББББББББББ

RxC high or low time (16X)

БББ

БББ

30

БББ

БББ

10

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

f

*RX

БББББББББББББББББББББ

БББББББББББББББББББББ

RxC Frequency (16X) (for higher speeds contact factory)

БББ

БББ

0

БББ

БББ

ББББ

ББББ

16

ББББ

ББББ

MHz

ББББ

ББББ

БББББББББББББББББББББ

БББББББББББББББББББББ

RxC Frequency (1x)

8, 9

БББ

БББ

0

БББ

БББ

ББББ

ББББ

1

ББББ

ББББ

MHz

ББББ

ББББ

t

*TX

БББББББББББББББББББББ

БББББББББББББББББББББ

TxC High or low time (16X)

БББ

БББ

30

БББ

БББ

15

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

f

*TX

БББББББББББББББББББББ

БББББББББББББББББББББ

TxC frequency (16X) (for higher speeds contact factory)

БББ

БББ

БББ

БББ

ББББ

ББББ

16

ББББ

ББББ

MHz

ББББ

БББББББББББББББББББББ

TxC frequency (1X)

8, 9

БББ

0

БББ

ББББ

1

ББББ

MHz

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

Transmitter Timing, external clock (See Figure 12)

ББББ

ББББ

t

*TXD

БББББББББББББББББББББ

БББББББББББББББББББББ

TxD output delay from TxC low (TxC input pin)

БББ

БББ

БББ

БББ

40

ББББ

ББББ

78

ББББ

ББББ

ns

ББББ

ББББ

t

*TCS

БББББББББББББББББББББ

БББББББББББББББББББББ

Output delay from TxC output pin low to TxD data output

БББ

БББ

БББ

БББ

8

ББББ

ББББ

30

ББББ

ББББ

ns