Philips SC28L91 User Manual

Page 15

Philips Semiconductors

Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

15

ББББ

ББББ

Unit

ББББ

ББББ

Max

БББ

БББ

Typ

БББ

БББ

Min

БББББББББББББББББББББ

БББББББББББББББББББББ

Parameter

ББББ

ББББ

Symbol

ББББББББББББББББББББББББББББББББББ

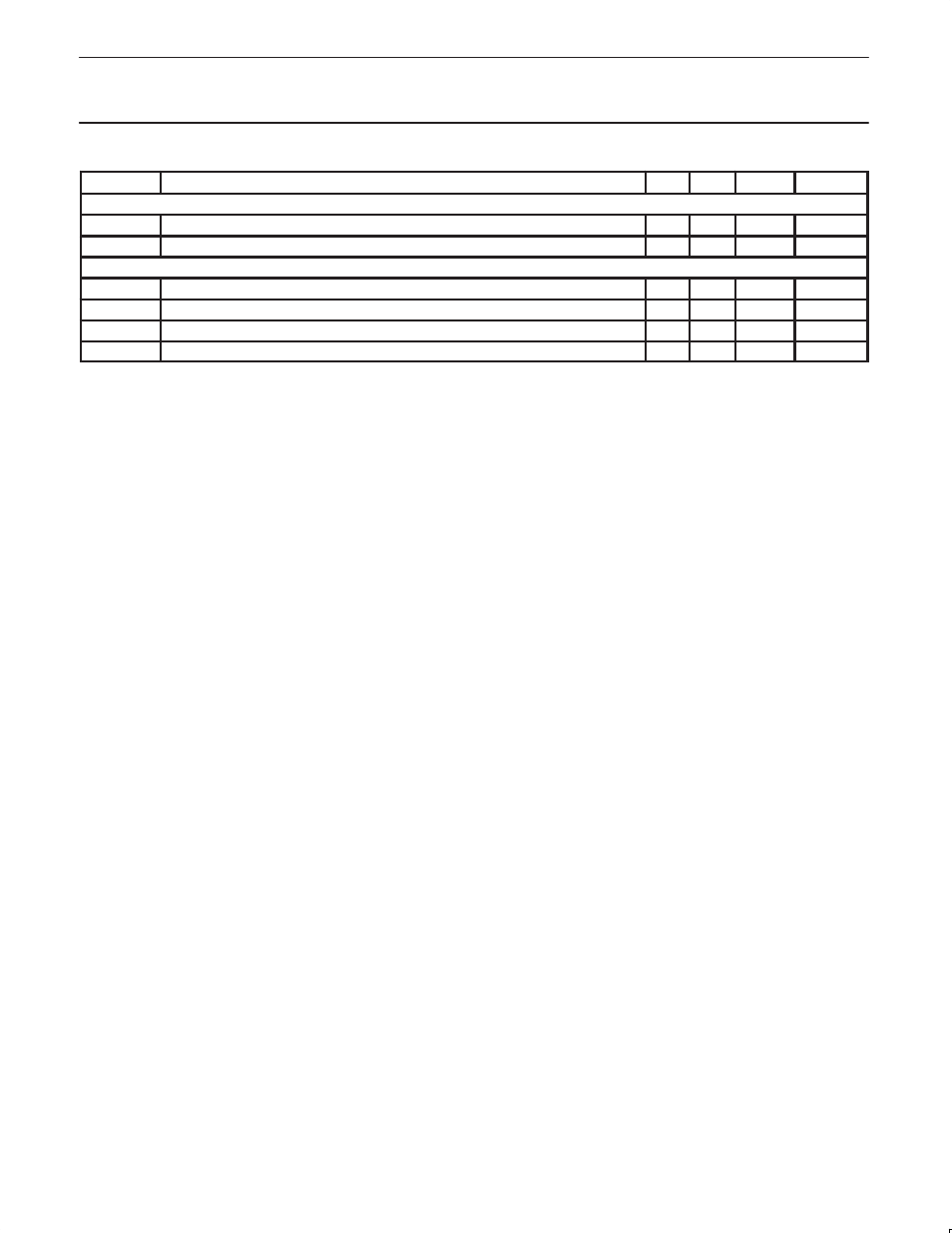

Receiver Timing, external clock (See Figure 13)

ББББ

ББББ

t

*RXS

БББББББББББББББББББББ

БББББББББББББББББББББ

RxD data setup time to RxC high

БББ

БББ

50

БББ

БББ

10

ББББ

ББББ

ББББ

ББББ

ns

ББББ

ББББ

t

*RXH

БББББББББББББББББББББ

БББББББББББББББББББББ

RxD data hold time from RxC high

БББ

БББ

50

БББ

БББ

10

ББББ

ББББ

ББББ

ББББ

ns

ББББББББББББББББББББББББББББББББББ

ББББББББББББББББББББББББББББББББББ

68000 or Motorola bus timing (See Figures 6, 7, 8)

10

ББББ

ББББ

t

DCR

БББББББББББББББББББББ

БББББББББББББББББББББ

DACKN Low (read cycle) from X1 High

10

БББ

БББ

БББ

БББ

18

ББББ

ББББ

57

ББББ

ББББ

ns

ББББ

ББББ

t

DCW

БББББББББББББББББББББ

БББББББББББББББББББББ

DACKN Low (write cycle) from X1 High

БББ

БББ

БББ

БББ

18

ББББ

ББББ

57

ББББ

ББББ

ns

ББББ

ББББ

t

DAT

БББББББББББББББББББББ

БББББББББББББББББББББ

DACKN High impedance from CEN or IACKN High

БББ

БББ

БББ

БББ

10

ББББ

ББББ

15

ББББ

ББББ

ns

ББББ

ББББ

t

CSC

БББББББББББББББББББББ

БББББББББББББББББББББ

CEN or IACKN setup time to X1 High for minimum DACKN cycle

БББ

БББ

30

БББ

БББ

10

ББББ

ББББ

ББББ

ББББ

ns

NOTES:

1. Parameters are valid over specified temperature and voltage range.

2. All voltage measurements are referenced to ground (GND). For testing, all inputs swing between 0.4 V and 3.0 V with a transition time of

5 ns maximum. For X1/CLK this swing is between 0.4 V and 0.8*V

CC

. All time measurements are referenced at input voltages of 0.8 V and

2.0 V and output voltages of 0.8 V and 2.0 V, as appropriate.

3. Test conditions for outputs: CL = 125 pF, except open drain outputs. Test conditions for open drain outputs: C

L

= 125 pF,

constant current source = 2.6 mA.

4. Typical values are the average values at +25

°

C and 3.3 V.

5. Timing is illustrated and referenced to the WRN and RDN Inputs. Also, CEN may be the “strobing” input. CEN and RDN (also CEN and

WRN) are ORed internally. The signal asserted last initiates the cycle and the signal negated first terminates the cycle.

6. Guaranteed by characterization of sample units.

7. If CEN is used as the “strobing” input, the parameter defines the minimum High times between one CEN and the next. The RDN signal must

be negated for t

RWD

to guarantee that any status register changes are valid.

8. Minimum frequencies are not tested but are guaranteed by design.

9. Clocks for 1X mode should maintain a 60/40 duty cycle or better.

10. Minimum DACKN time is t

DCR

= t

DSC

+ t

DCR

+ two positive edges of the X1 clock. For faster bus cycles, the 80XXX bus timing may be used

while in the 68XXX mode. It is not necessary to wait for DACKN to insure the proper operation of the SC28C91. In all cases the data will be

written to the SC28L91 on the falling edge of DACKN or the rise of CEN. The fall of CEN initializes the bus cycle. The rise of CEN ends the

bus cycle. DACKN low or CEN high completes the write cycle.