Philips SC28L91 User Manual

Page 30

Philips Semiconductors

Product data sheet

SC28L91

3.3 V or 5.0 V Universal Asynchronous

Receiver/Transmitter (UART)

2004 Oct 21

30

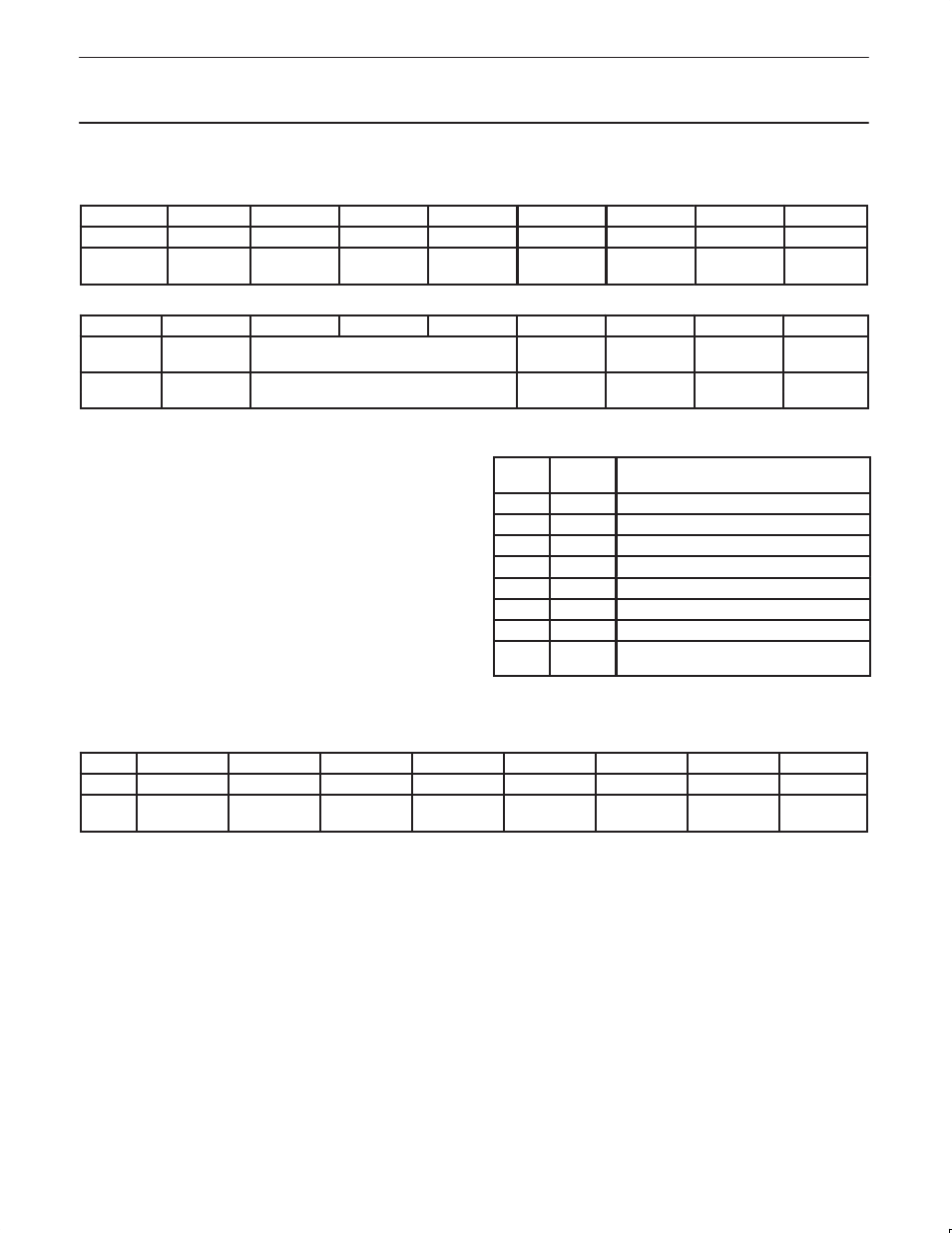

OPR Output Port Register

The output pins (OP pins) drive the compliment of the data in this register as controlled by SOPR and ROPR.

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

N/A

OP 7

OP 6

OP 5

OP 4

OP 3

OP 2

OP 1

OP 0

N/A

0 = Pin High

0 = Pin High

0 = Pin High

0 = Pin High

0 = Pin High

0 = Pin High

0 = Pin High

0 = Pin High

1 = Pin Low

1 = Pin Low

1 = Pin Low

1 = Pin Low

1 = Pin Low

1 = Pin Low

1 = Pin Low

1 = Pin Low

ACR Auxiliary Control Register

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ACR

BRG SET

Select

Counter Timer Mode

Mode and clock sour select

Delta IP3 int

enable

Delta IP3 int

enable

Delta IP3 int

enable

Delta IP3 int

enable

0x04

0 = set 1

See table 7

0 = off

0 = off

0 = off

0 = off

1 = set 2

1 = enabled

1 = enabled

1 = enabled

1 = enabled

ACR—Auxiliary Control Register

ACR[7]—Baud Rate Generator Set Select

This bit selects one of two sets of baud rates to be generated by the

BRG (see Table 5).

The selected set of rates is available for use by the receiver and

transmitter as described in CSR. Baud rate generator characteristics

are given in Table 6.

ACR[6:4]—Counter/Timer Mode And Clock Source Select

This field selects the operating mode of the counter/timer and its

clock source as shown in Table 7

ACR[3:0]—IP3, IP2, IP1, IP0 Change-of-State Interrupt Enable

This field selects which bits of the input port change register (IPCR)

cause the input change bit in the interrupt status register (ISR [7]) to

be set. If a bit is in the ‘on’ state the setting of the corresponding bit

in the IPCR will also result in the setting of ISR [7], which results in

the generation of an interrupt output if IMR [7] = 1. If a bit is in the

‘off’ state, the setting of that bit in the IPCR has no effect on ISR [7].

Table 7. ACR 6:4 field definition

ACR

6:4

MODE

CLOCK SOURCE

000

Counter

External (IP2)

001

Counter

TxC – 1X clock of transmitter

010

reserved

011

Counter

Crystal or X1/CLK clock divided by 16

100

Timer

External (IP2)

101

Timer

External (IP2) divided by 16

110

Timer

Crystal or external clock (X1/CLK)

111

Timer

Crystal or external clock (X1/CLK) divided

by 16

NOTE:

1. The timer mode generates a square wave

IPCR Input Port change Register

Addr

Bit 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

IPCR

Delta IP3

Delta IP3

Delta IP3

Delta IP3

IP 3

IP 2

IP 1

IP 0

0x04

0 = no change

0 = no change

0 = no change

0 = no change

0 = low

0 = low

0 = low

0 = low

1 = change

1 = change

1 = change

1 = change

1 = High

1 = High

1 = High

1 = High

IPCR[7:4]—IP3, IP2, IP1, IP0 Change-of-State

These bits are set when a change-of-state, as defined in the input

port section of this data sheet, occurs at the respective input pins.

They are cleared when the IPCR is read by the CPU. A read of the

IPCR also clears ISR [7], the input change bit in the interrupt status

register. The setting of these bits can be programmed to generate

an interrupt to the CPU.

IPCR[3:0]—IP3, IP2, IP1, IP0 Change-of-State

These bits provide the current state of the respective inputs. The

information is unlatched and reflects the state of the input pins at the

time the IPCR is read.