Datasheet – SMSC LAN9312 User Manual

Page 193

High Performance Two Port 10/100 Managed Ethernet Switch with 32-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9312

193

Revision 1.4 (08-19-08)

DATASHEET

12

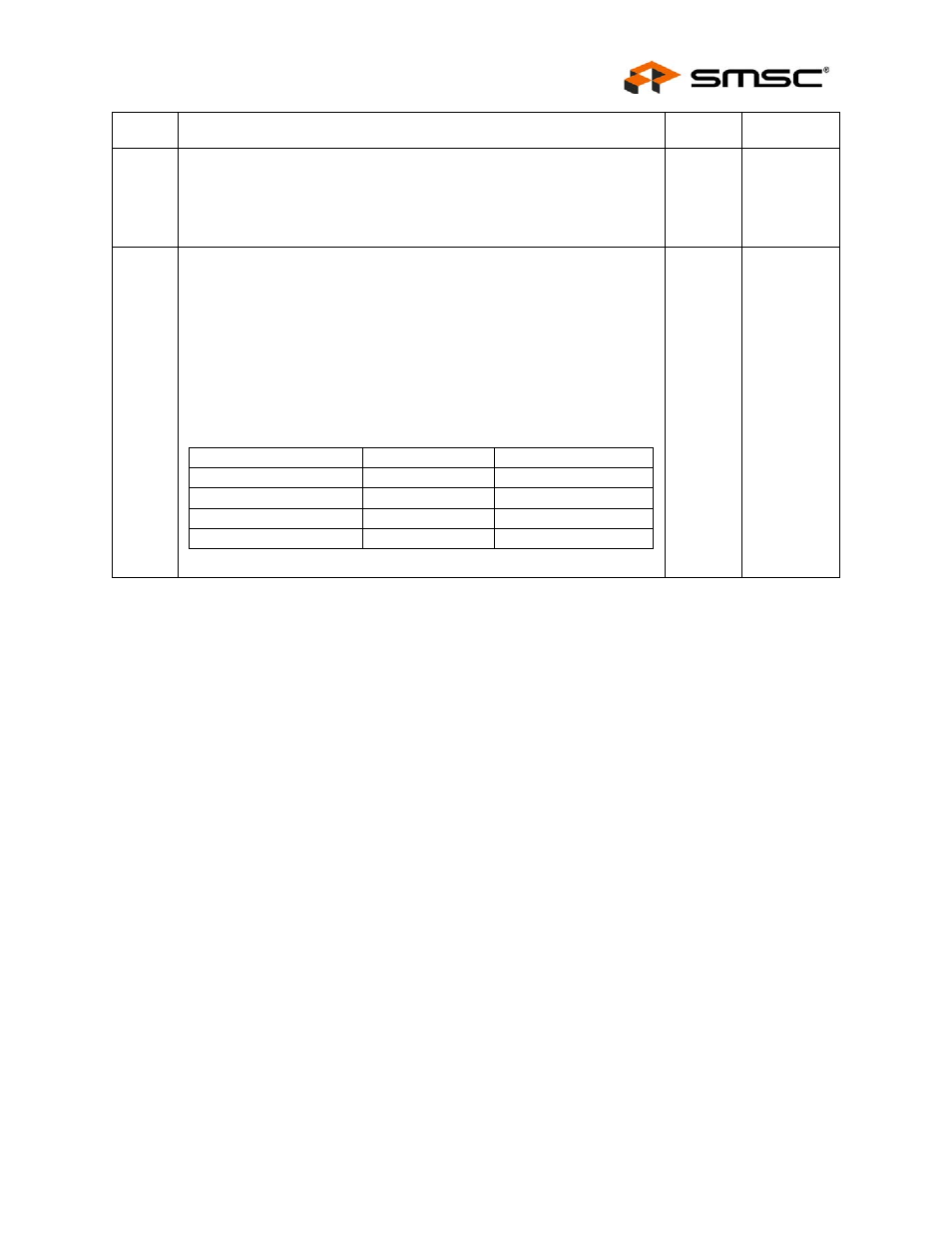

GPIO 8 Clock Event Polarity (GPIO_EVENT_POL_8)

This bit determines if the 1588 clock event output on GPIO 8 is active high

or low.

0: 1588 clock event output active low

1: 1588 clock event output active high

R/W

1b

11:0

GPIO Buffer Type 11-0 (GPIOBUF[11:0])

This field sets the buffer types of the 12 GPIO pins.

0: Corresponding GPIO pin configured as an open-drain driver

1: Corresponding GPIO pin configured as a push/pull driver

As an open-drain driver, the output pin is driven low when the corresponding

data register is cleared, and is not driven when the corresponding data

register is set.

As an open-drain driver used for 1588 Clock Events, the corresponding

GPIO_EVENT_POL_8 and GPIO_EVENT_POL_9 bits determine when the

corresponding pin is driven per the following table:

R/W

0h

BITS

DESCRIPTION

TYPE

DEFAULT

GPIOx Clock Event Polarity

1588 Clock Event

Pin State

0

no

not driven

0

yes

driven low

1

no

driven low

1

yes

not driven