Smi and nmi routing, Power connector, Speaker – Intel ISP1100 User Manual

Page 19

Description

19

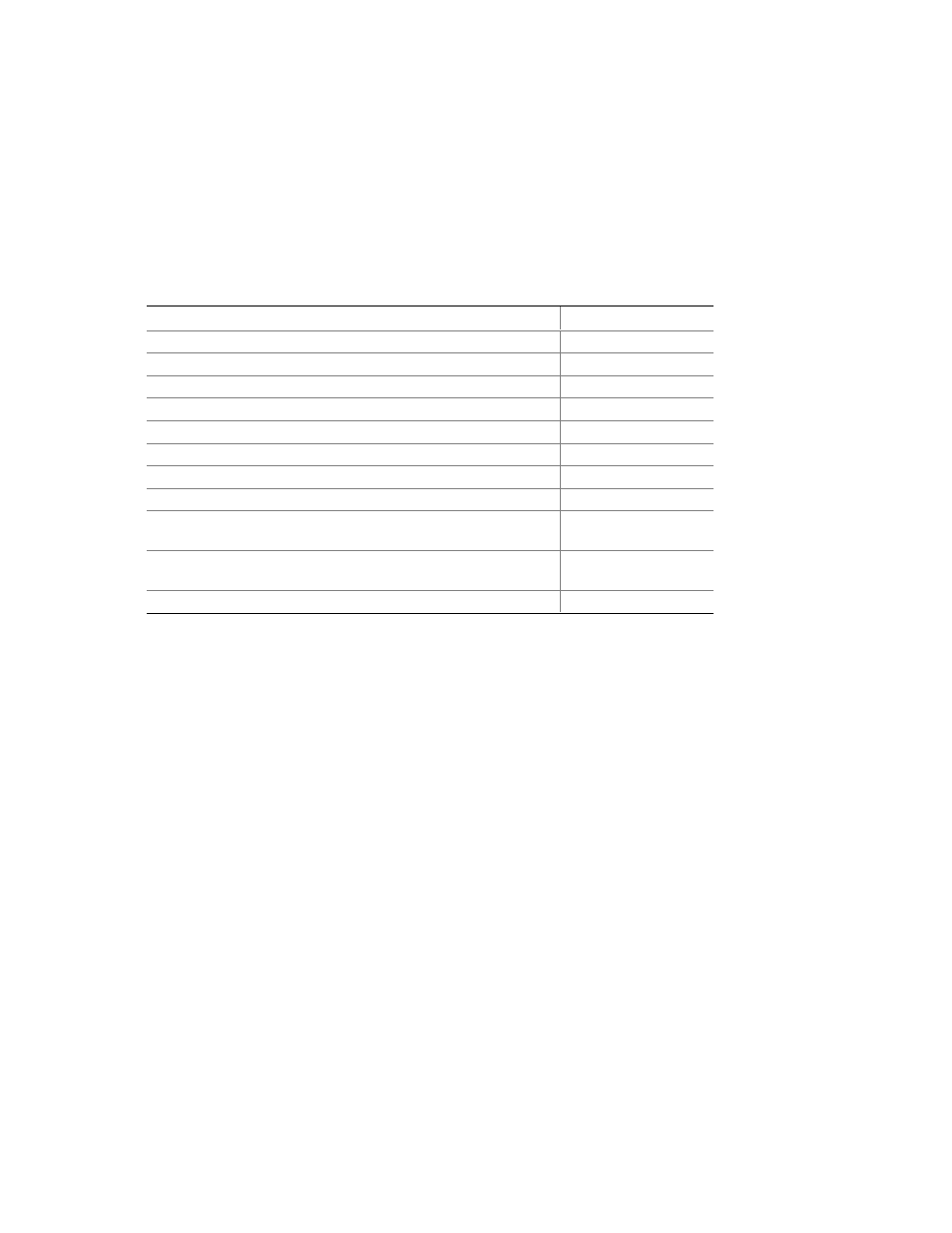

SMI and NMI Routing

There are numerous SMI sources and all are routed to the PIIX4. Software must configure the

PIIX4 SMI source pins to control whether SMI is propagated through to the processor via its

H_SMI input or not. For details on the fault conditions that cause SMI to occur, consult the data

sheets of the SMI source ICs. The SMI routing on the server board is described in Table 6. Note

that some PIIX4 inputs have several sources. Schematic signal names are in parenthesis.

Table 6.

SMI and NMI Routing

SMI Source

PIIX4 Input Pin

BX Chipset PCI SERR# - used for ECC Errors (P_SERR#)

EXT_SMI#

LAN PCI SERR# (P_SERR#)

EXT_SMI#

All three PCI Slot’s SERR# (P_SERR#)

EXT_SMI#

Gluechips EXTSMI# output – used for +5 VSB errors

GPI13

Gluechips EXTSMI# output – Through buffer to (P_SERR#)

EXT_SMI#

LAN1 PCI PME# (P_PME#)

GPI1

LAN2 PCI PME# (P_PME#)

GPI1

All three PCI slot’s PME# (P_PME#)

GPI1

Super I

/

O Serial Interrupt SMI – used for watchdog timer

(SER_IRQ)

SER_IRQ

Super I

/

O PME# (SIO_RIA#) – originally from WOR header or

ext. modem

RIAB

Wake on LAN header – used for Wake on LAN (WOL#)

LID

The Gluechips EXT_SMI# output is also connected to the PIIX4 GPI13 pin to provide a status of

the Gluechips EXT_SMI# signal.

All NMI generation on the server board is under software control. Writes to PIIX4 GPO17 are

routed to the PIIX4 IOCHK# input which may be configured to cause a NMI to occur. Thus,

software may cause a NMI to occur by pulsing GPO17 active.

The TR440BX server board BIOS SMI handler detects SMI events, logs the events, and elevates

selected events to NMI level.

Power Connector

When used with an ATX-compliant power supply that supports remote power on/off, the server

board can turn off the system power through software control.

Speaker

A 47-ohm inductive speaker is mounted on the server board. The speaker provides audible error

code (beep code) information during the Power-On Self-Test (POST).