Bit proprietary f, Mc-8l family, Support tools – FUJITSU Semiconductor User Manual

Page 74

73

8-bit Proprietary F

2

MC-8L Family

Support Tools

F

2

MC-8LF

amily

Support tools

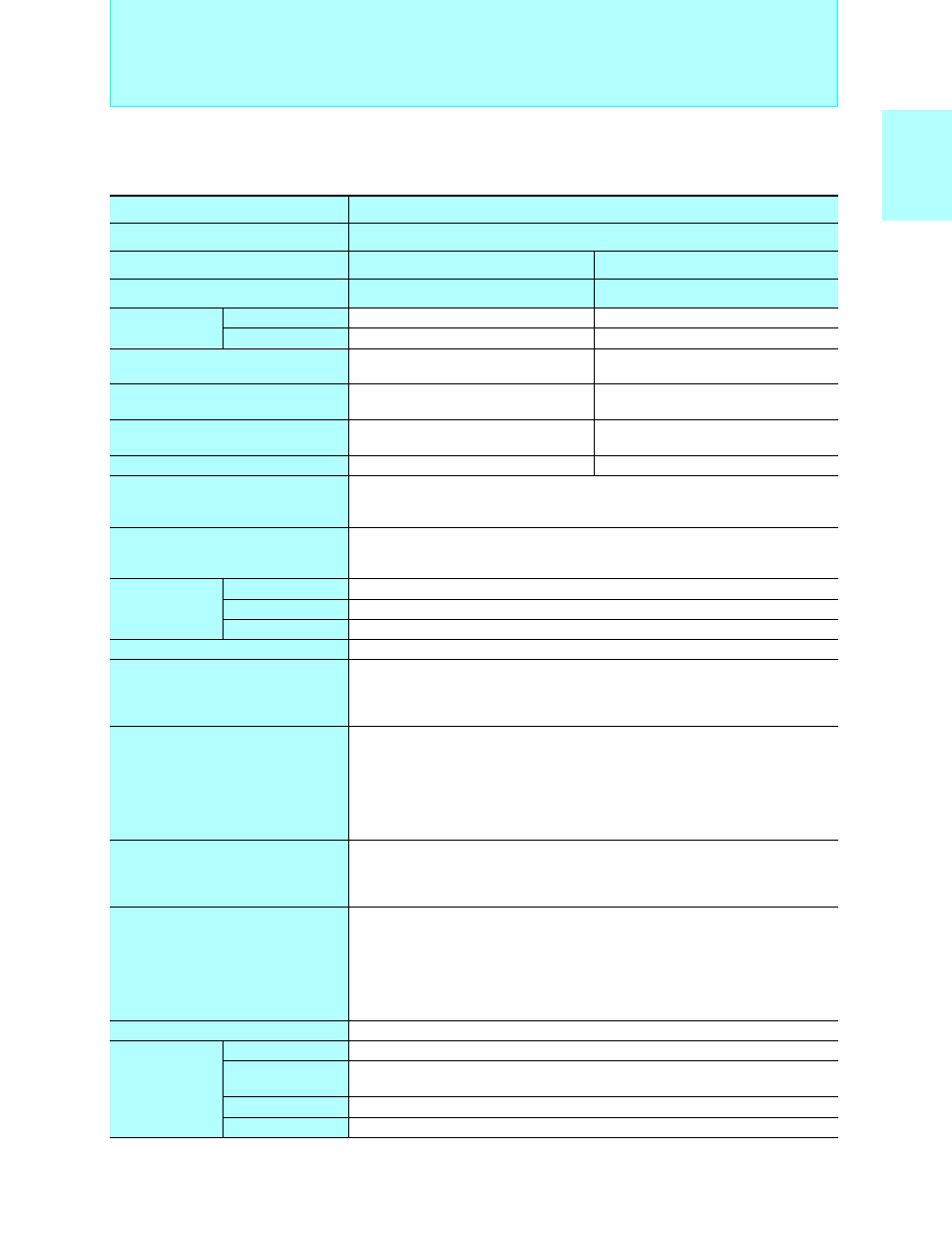

Emulator specification for F

2

MC-8L

(Continued)

Emulator series

MB2140 series emulator

Main unit

Main unit : MB2141B

Pod

MB2144-508

MB2144-505

Target microcontroller

F

2

MC-8L

F

2

MC-8L

Evaluation device

Old

Yes

Yes

New

Yes

No

Operating power supply voltage of micro-

controller *

2.7 to 5.5 V

2.7 to 5.5 V

Operating frequency of microcontroller *

Internal : 32 kHz to 20 MHz

External : 8 kHz to 5 MHz

Internal : 32 kHz to 16 MHz

External : 8 kHz to 4 MHz

Debugger / OS

S

OFTUNE

V3 Workbench

WindowsXP/Me/2000/98/NT4.0

S

OFTUNE

V3 Workbench

WindowsXP/Me/2000/98/NT4.0

Simple target

Attachment (MB89T625)

No

Memory area

- User’s memory area

- Emulation memory area

- Undefined area

User's memory area

- Max 20 area

- Unrestricted of area size

- READ, WRITE : an access attribute setup is possible.

Emulation area

Size

64 Kbyte

Mapping unit

1 byte unit, 20area

Access attribute

READ, WRITE, GUARD, NOGUARD

Mirror area : It is used at on-the-fly.

It is 5 area in all about copy area of user’s memory area and emulation memory area.

Execution control

- Continuous execution- The automatic change by sauce display

- Step execution- 1 step execution of a sub routine and a function

- Machine language command unit- Permission/prohibition of interrupt

- C language sauce line unit- Permission/prohibition of a watch dog reset function

Break

- Instruction execution break : 64 K point

- Data access break : 64 K point

- Sequential end break

- Garded access break

- Trace buffer full break

- Performance buffer full break

- Forced break

Trace capacity

- Single trace : 32 K cycles

(ON/OFF of trace by the event trigger and the sequencer is possible.)

- Multi trace : 2 K blocks

(1 block is 8 cycles before and after an event trigger.)

Trace data

- Address

- Data

- Status

Access status : READ, WRITE, CODE

Inside status of a device : reset, a hold, and data are effective/invalid.

- External probe data

- The execution level of a sequencer

Display form oftrace data

- Machine cycle

- Instruction mnemonic

- Sauce line

Event trigger con-

dition setup

The number of points

8

Trigger conditions

- The AND conditions of address, data, external probe and status.

- All conditions can be specified of don’t care per 1 bit.

Sequential level

8

Trigger path

Max 16M time