Digital signal processor hi-perion family, Hi-perion family – FUJITSU Semiconductor User Manual

Page 274

273

Digit

a

l sig

nal

processor

■

Hi-Perion Family

Packages: P - plastic, C - ceramic

Part

Number

Operating

Power Supply

Voltage(V)

Package

Features

QFP

PGA

MB86330

3.3 single

256C

Fixed point operations: Multiplication

16bit

×

16bit

→

31bit

Addition

40bit

+

40bit

→

40bit

Sum of products 40bit

±

16bit

×

16 bit

→

40bit

Processing performance 100MIPS max.

Data RAM: dual-port simultaneous access structure

Supports external RAM (ERAM)

Uses memory-mapped I/O (I/O is assigned to addresses in the memory space.)

Instruction RAM

←

48KW x 16-bit

Table RAM

←

16KW x 16-bit

Addressing:

Two independent addressing units

Eight general-purpose registers

Register-update addressing

Circular addressing

Two address update registers

MB86331

3.3 single

208P

Fixed point operations: Multiplication

16bit

×

16bit

→

31bit

Addition

40bit

+

40bit

→

40bit

Sum of products 40bit

±

16bit

×

16bit

→

40bit

Processing performance 80MIPS [email protected] V

Data RAM: dual-port simultaneous access structure

Supports external RAM (ERAM)

Uses memory-mapped I/O (I/O is assigned to addresses in the memory space.)

Instruction RAM

←

62KW x 16-bit

Table RAM

←

20KW x 16-bit

Addressing:

Two independent addressing units

Eight general-purpose registers

Register-update addressing

Circular addressing

Two address update registers

MB86335

3.3 single

208P

Fixed point operations: Multiplication

16bit

×

16bit

→

31bit

Addition

40bit

+

40bit

→

40bit

Sum of products 40bit

±

16bit

×

16bit

→

40bit

Processing performance 120MIPS [email protected] V

Data RAM: dual-port simultaneous access structure

Supports external RAM (ERAM)

Uses memory-mapped I/O (I/O is assigned to addresses in the memory space.)

Instruction RAM

←

62KW x 16-bit

Table RAM

←

32KW x 16-bit

Addressing:

Two independent addressing units

Eight general-purpose registers

Register-update addressing

Circular addressing

Two address update registers

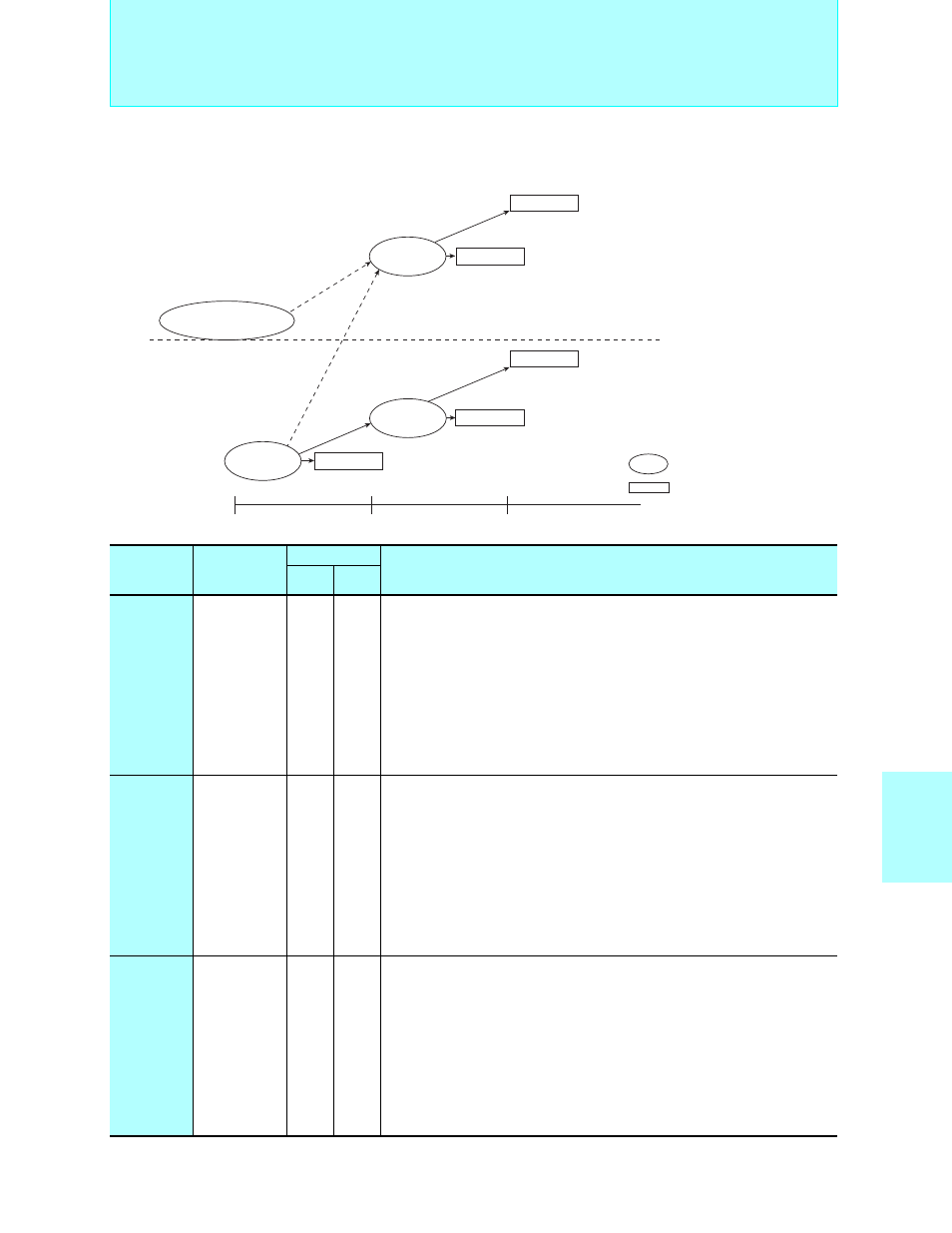

32 bit-DSP

16 bit-DSP

Firm ware Transfer

AC-3, MPEG-Audio, etc.

Firm ware on MUCAP

Hi-Perion1

100 MIPS

MB86330/331

Hi-Perion32

100 MIPS~

Hi-Perion2

120 MIPS

MB86345

32 bit Enhance

Hard-Macro

Hard-Macro

Hard-Macro

Hard-Macro

Hard-Macro

'98

'99

'2000

PDC, G.lite (0.25 µ 0.3~0.4 mW/[email protected] V)

: DSP core(RAM version DSP)

: Hard-Macro(System LSI)

W-CDMA, PDC

(0.25 µ 0.12 mW/[email protected] V)

W-CDMA, PDC

(0.25 µ MT-CMOS

0.15 mW/[email protected] V)

DVD, AV-Receiver

(0.25 µ 80 MIPS)@2.5V

DTV

(0.25 µ 120 MIPS)@2.5V

MB86335

Digital Signal Processor Hi-Perion Family