Table 11. clock control registers (continued) – Rainbow Electronics MAX98088 User Manual

Page 82

Stereo Audio Codec

with FLEXSOUND Technology

MAX98088

82

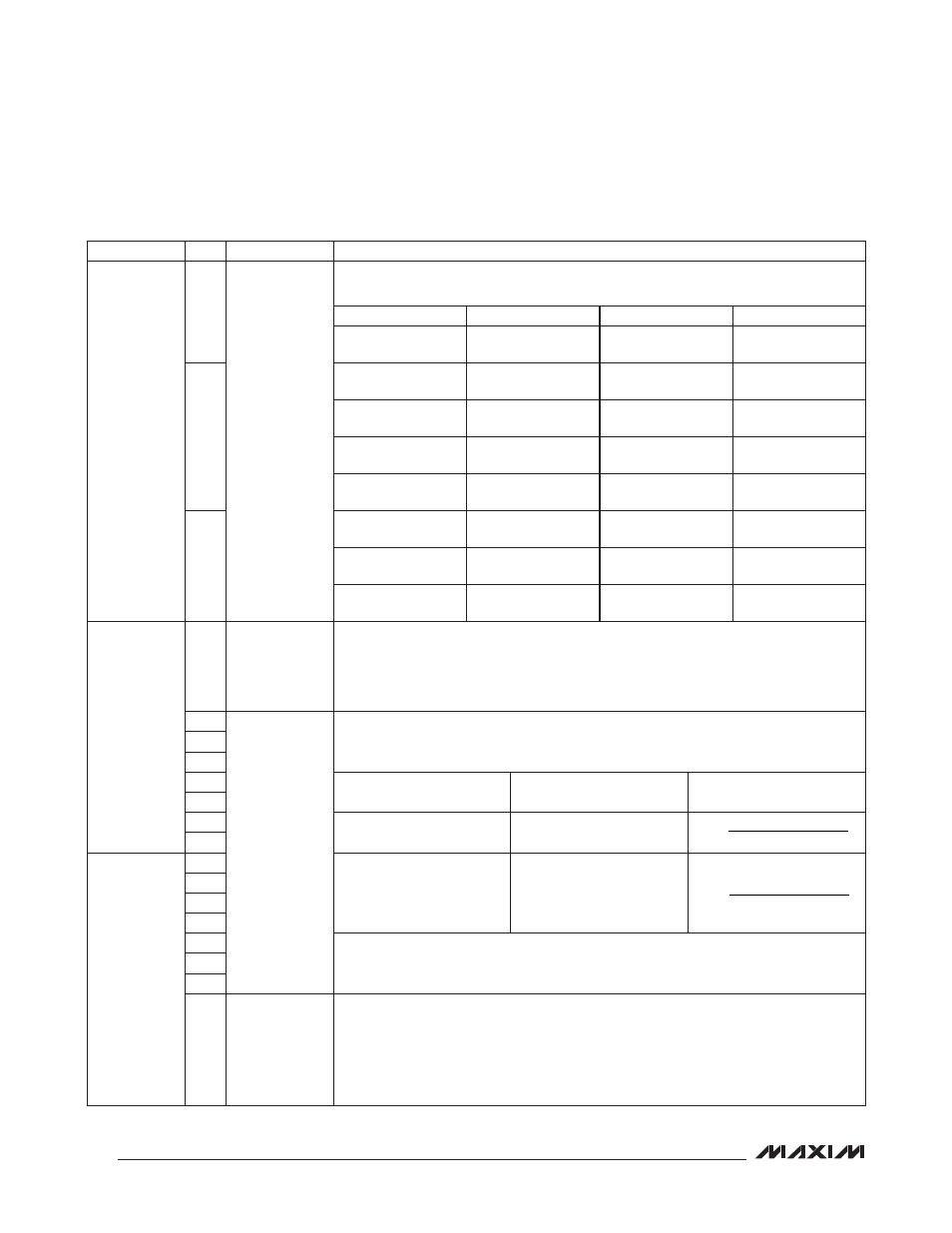

Table 11. Clock Control Registers (continued)

REGISTER

BIT

NAME

DESCRIPTION

0x11

3

FREQ1

Exact Integer Mode

Overrides PLL1 and NI1 and configures a specific PCLK to LRCLK ratio.

VALUE

SAMPLE RATE

VALUE

SAMPLE RATE

0x0

Disabled

0x8

PCLK = 12MHz,

LRCLK = 8kHz

2

0x1

Reserved

0x9

PCLK = 12MHz,

LRCLK = 16kHz

0x2

Reserved

0xA

PCLK = 13MHz,

LRCLK = 8kHz

0x3

Reserved

0xB

PCLK = 13MHz,

LRCLK = 16kHz

0x4

Reserved

0xC

PCLK = 16MHz,

LRCLK = 8kHz

1

0x5

Reserved

0xD

PCLK = 16MHz,

LRCLK = 16kHz

0x6

Reserved

0xE

PCLK = 19.2MHz,

LRCLK = 8kHz

0x7

Reserved

0xF

PCLK = 19.2MHz,

LRCLK = 16kHz

0x12/0x1A

7

PLL1/PLL2

PLL Mode Enable (Slave Mode Only)

PLL1/PLL2 enables a digital PLL that locks on to the externally supplied LRCLK

frequency and automatically sets the LRCLK divider (NI1/NI2).

0 = Disabled

1 = Enabled

6

NI1/

NI2

Normal Mode LRCLK Divider

When PLL1/PLL2 = 0, the frequency of LRCLK is determined by NI1/NI2. See Table 12

for common NI values.

5

4

3

SAMPLE RATE

DHF1/DHF2

NI1/NI2 FORMULA

2

1

8kHz P LRCLK P 48kHz

0

0

0x13/0x1B

7

48kHz

< LRCLK P 96kHz

1

6

5

4

3

f

LRCLK

= LRCLK frequency

f

PCLK

= Prescaled MCLK frequency (PCLK)

2

1

0

NI1[0]/NI2[0]

Rapid Lock Mode

Program NI1/NI2 to the nearest valid ratio and set NI1[0]/NI2[0] when PLL1/PLL2 = 1

to enable rapid lock mode. Normally, the PLL automatically calculates and dynamically

adjusts NI1/NI2. When rapid lock mode is properly configured, the PLL starting point is

much closer to the correct value, thus speeding up lock time. Wait one LRCLK period

after programming NI1/NI2 before setting PLL1/PLL2 = 1.

LRCLK

PCLK

65536 96 f

NI

f

Ч

Ч

=

LRCLK

PCLK

65536 48 f

NI

f

Ч

Ч

=