Table 10. digital audio interface registers – Rainbow Electronics MAX98088 User Manual

Page 76

Stereo Audio Codec

with FLEXSOUND Technology

MAX98088

76

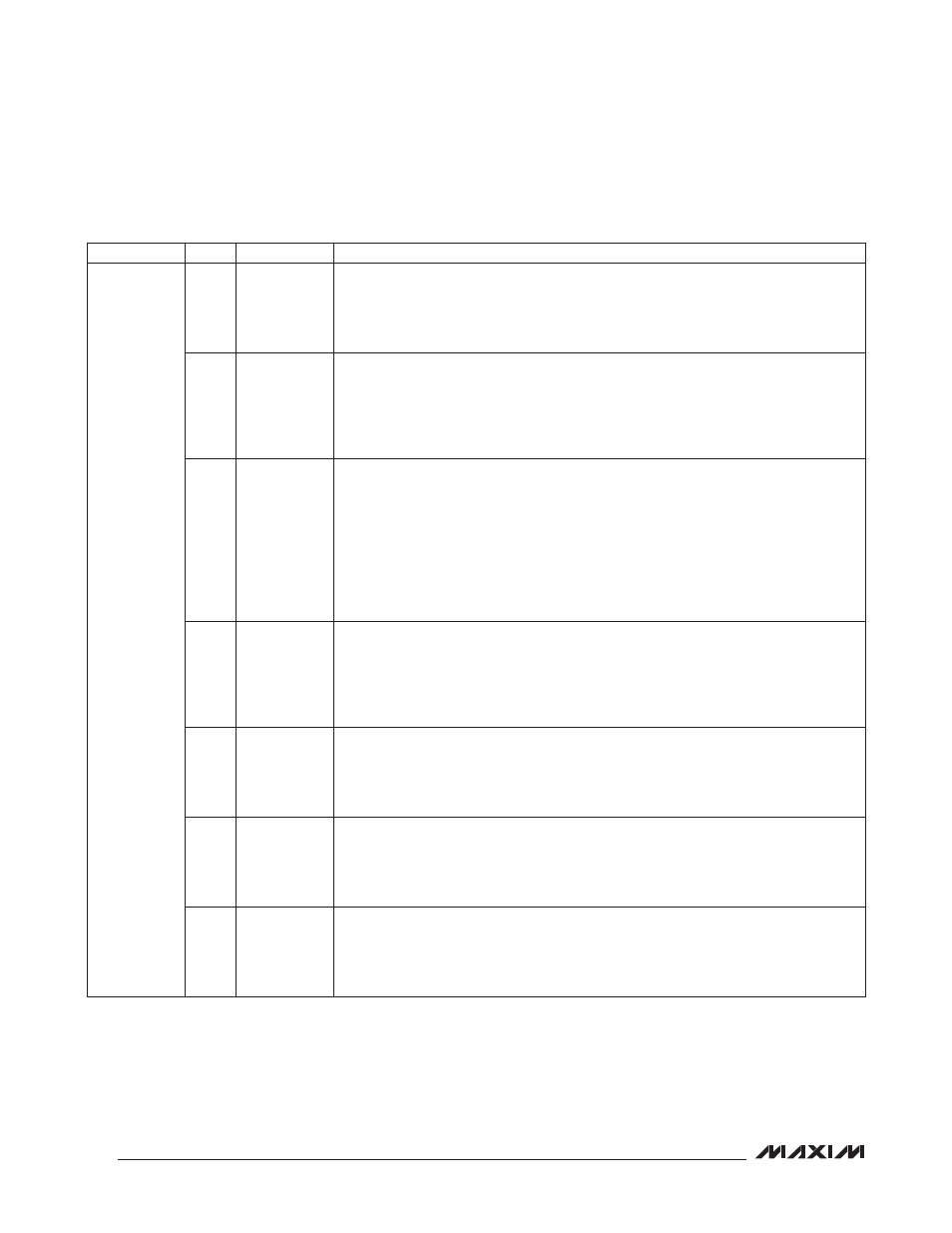

Table 10. Digital Audio Interface Registers

REGISTER

BIT

NAME

DESCRIPTION

0x14/0x1C

7

MAS1/MAS2

DAI1/DAI2 Master Mode

In master mode, DAI1/DAI2 outputs LRCLK and BCLK. In slave mode, DAI1/DAI2

accept LRCLK and BCLK as inputs.

0 = Slave mode

1 = Master mode

6

WCI1/WCI2

DAI1/DAI2 Word Clock Invert

TDM1/TDM2 = 0:

0 = Left-channel data is transmitted while LRCLK is low.

1 = Right-channel data is transmitted while LRCLK is low.

TDM1/TDM2 = 1:

Always set WCI = 0.

5

BCI1/BCI2

DAI1/DAI2 Bit Clock Invert

BCI1/BCI2 must be set to 1 when TDM1/TDM2 = 1.

0 = SDIN is accepted on the rising edge of BCLK.

SDOUT is valid on the rising edge of BCLK.

1 = SDIN is accepted on the falling edge of BCLK.

SDOUT is valid on the falling edge of BCLK.

Master Mode:

0 = LRCLK transitions on the falling edge of BCLK.

1 = LRCLK transitions on the rising edge of BCLK.

4

DLY1/DLY2

DAI1/DAI2 Data Delay

DLY1/DLY2 has no effect when TDM1/TDM2 = 1.

0 = The most significant data bit is clocked on the first active BCLK edge after an

LRCLK transition.

1 = The most significant data bit is clocked on the second active BCLK edge after an

LRCLK transition.

2

TDM1/TDM2

DAI1/DAI2 Time-Division Multiplex Mode (TDM Mode)

Set TDM1/TDM2 when communicating with devices that use a frame synchronization

pulse on LRCLK instead of a square wave.

0 = Disabled

1 = Enabled (BCI1/BCI2 must be set to 1)

1

FSW1/FSW2

DAI1/DAI2 Wide Frame Sync Pulse

Increases the width of the frame sync pulse to the full data width when TDM1/TDM2 =

1. FSW1/FSW2 has no effect when TDM1/TDM2 = 0.

0 = Disabled

1 = Enabled

0

WS1/WS2

DAI1/DAI2 Audio Data Bit Depth

Determines the maximum bit depth of audio being transmitted and received. Data is

always 16 bit when TDM1/TMD2 = 0.

0 = 16 bits

1 = 24 bits