Device status, Table 35. status and interrupt registers – Rainbow Electronics MAX98088 User Manual

Page 111

Stereo Audio Codec

with FLEXSOUND Technology

MAX98088

111

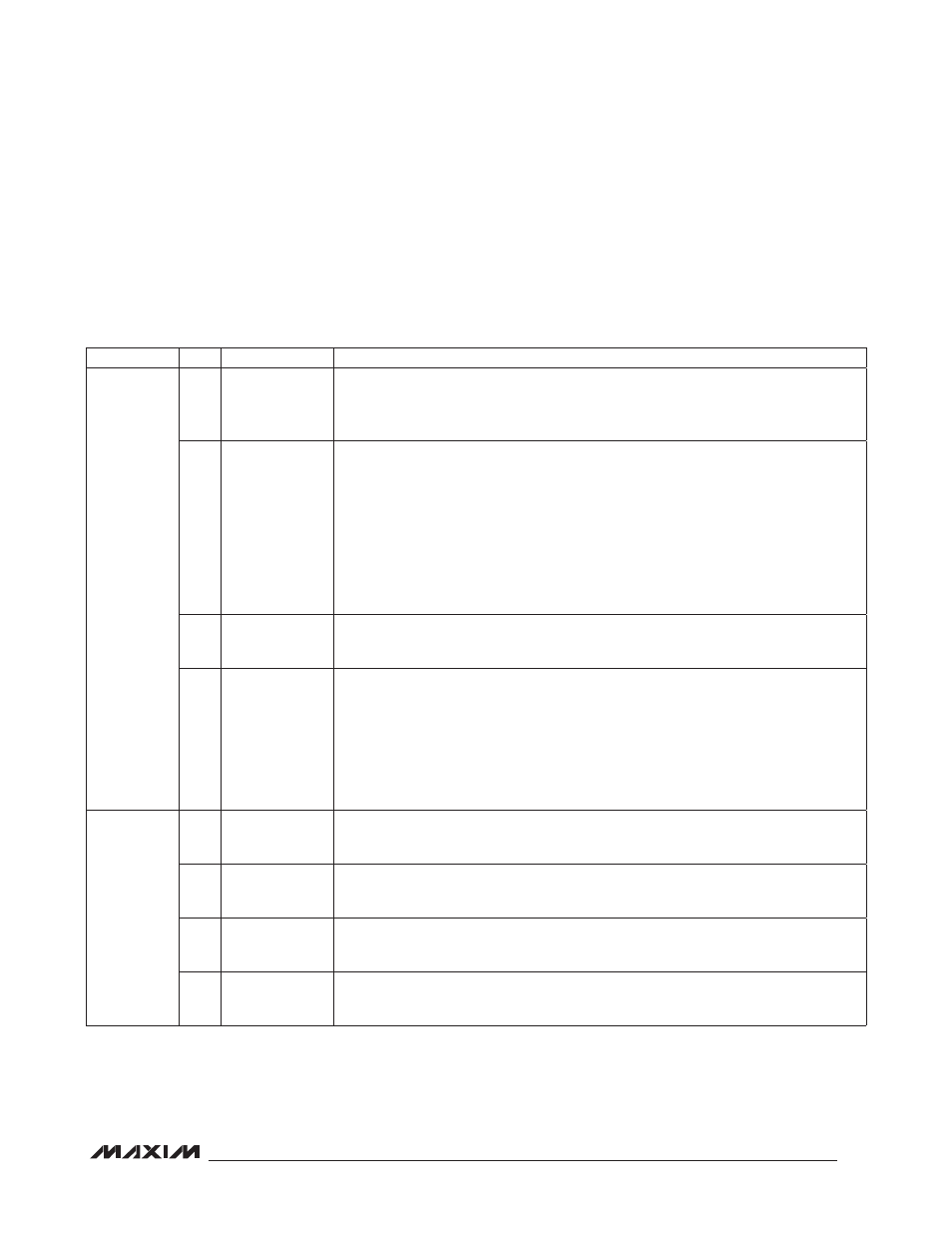

Table 35. Status and Interrupt Registers

Device Status

The IC uses register 0x00 and IRQ to report the status of

various device functions. The status register bits are set

when their respective events occur, and cleared upon

reading the register. Device status can be determined

either by poling register 0x00 or configuring the IRQ to

pull low when specific events occur. IRQ is an open-

drain output that requires a pullup resistor for proper

operation. Register 0x0F determines which bits in the

status register trigger IRQ to pull low.

REGISTER

BIT

NAME

DESCRIPTION

0x00

(Read Only)

7

CLD

Full Scale

0 = All digital signals are less than full scale.

1 = The DAC or ADC signal path has reached or exceeded full scale. This typically

indicates clipping.

6

SLD

Volume Slew Complete

SLD reports that any of the programmable-gain arrays or volume controllers has

completed slewing from a previous setting to a new programmed setting. If multiple

gain arrays or volume controllers are changed at the same time, the SLD flag is set

after the last volume slew completes. SLD also reports when the digital audio interface

soft-start or soft-stop process has completed. MCLK is required for proper SLD

operation.

0 = No volume slewing sequences have completed since the status register was last

read.

1 = Volume slewing complete.

5

ULK

Digital Audio Interface Unlocked

0 = Both digital audio interfaces are operating normally.

1 = Either digital audio interface is configured incorrectly or receiving invalid data.

1

JDET

Jack Configuration Change

JDET reports changes to any bit in the Jack Status register (0x02). Changes to the Jack

Status bits are debounced before setting JDET. The debounce period is programmable

using the JDEB bits. JDET is always set the first time JDETEN or SHDN is set the first

time power is applied to the IC. Read the status register following such an event to clear

JDET and allow for proper jack detection.

0 = No change in jack configuration.

1 = Jack configuration has changed.

0x0F

7

ICLD

Full-Scale Interrupt Enable

0 = Disabled

1 = Enabled

6

ISLD

Volume Slew Complete Interrupt Enable

0 = Disabled

1 = Enabled

5

IULK

Digital Audio Interface Unlocked Interrupt Enable

0 = Disabled

1 = Enabled

1

IJDET

Jack Configuration Change Interrupt Enable

0 = Disabled

1 = Enabled