Figure 10-4. filter example – National Instruments DAQ M Series User Manual

Page 119

Chapter 10

Digital Routing and Clock Generation

10-10

ni.com

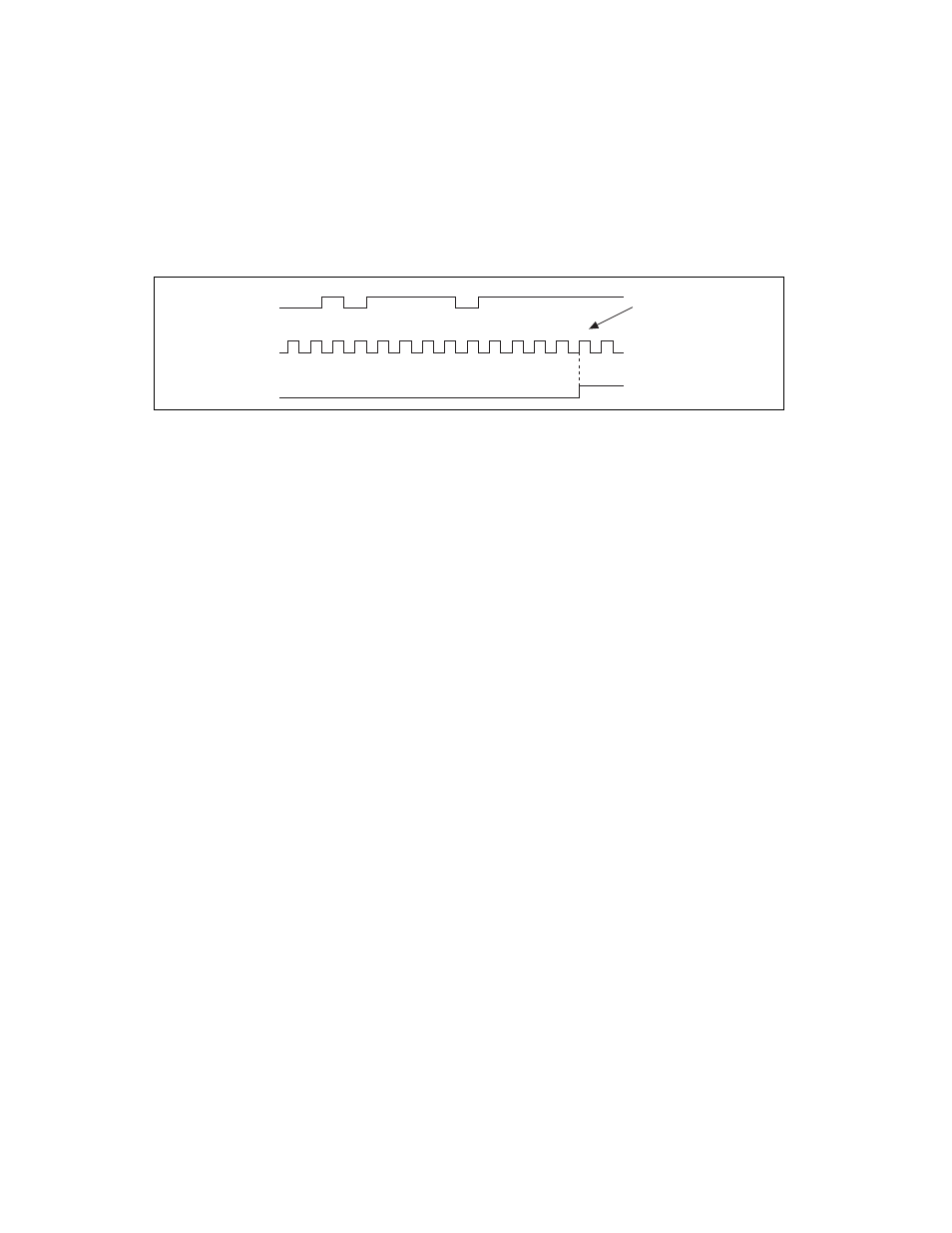

The filter setting for each input can be configured independently. On power

up, the filters are disabled. Figure 10-4 shows an example of a low to high

transition on an input that has its filter set to 125 ns (N = 5).

Figure 10-4. Filter Example

Enabling filters introduces jitter on the input signal. For the 125 ns and

6.425 µs filter settings, the jitter is up to 25 ns. On the 2.55 ms setting, the

jitter is up to 10.025 µs.

When a PFI input is routed directly to RTSI, or a RTSI input is routed

directly to PFI, the M Series device does not use the filtered version of the

input signal.

Refer to the KnowledgeBase document, Digital Filtering with M Series, for

more information about digital filters and counters. To access this

KnowledgeBase, go to

ni.com/info

and enter the info code

rddfms

.

1

2

3

1

4

1

2

3

4

5

RTSI, PFI, or

PXI_STAR Terminal

Filter Clock

(40 MHz)

Filtered Input

Filtered input goes high

when terminal is sampled

high on five consecutive

filter clocks.