Intel AS/400 RISC Server User Manual

Page 362

5308.3

4550

4550

12

8 MB

262

740-2070 (1513)

4270

3660

4550

12

8 MB

262

740-2070 (1512)

2333.3

2000

4550

12

8 MB

262

740-2070 (1511)

1225

1050

4550

12

8 MB

262

740-2070 (1510)

140

120

4550

12

8 MB

262

740-2070 (Base)

4270

3660

3660

8

8 MB

262

740-2069 (1512)

2333.3

2000

3660

8

8 MB

262

740-2069 (1511)

1225

1050

3660

8

8 MB

262

740-2069 (1510)

140

120

3660

8

8 MB

262

740-2069 (Base)

2333.3

2000

2890

8

4 MB

262

730-2068 (1511)

1225

1050

2890

8

4 MB

262

730-2068 (1510)

653.3

560

2890

8

4 MB

262

730-2068 (1509)

280

240

2890

8

4 MB

262

730-2068 (1508)

81.7

70

2890

8

4 MB

262

730-2068 (Base)

2333.3

2000

2000

4

4 MB

262

730-2067 (1511)

1225

1050

2000

4

4 MB

262

730-2067 (1510)

653.3

560

2000

4

4 MB

262

730-2067 (1509)

280

240

2000

4

4 MB

262

730-2067 (1508)

81.7

70

2000

4

4 MB

262

730-2067 (Base)

1225

1050

1050

2

4 MB

262

730-2066 (1510)

653.3

560

1050

2

4 MB

262

730-2066 (1509)

280

240

1050

2

4 MB

262

730-2066 (1508)

140

120

1050

2

4 MB

262

730-2066 (1507)

81.7

70

1050

2

4 MB

262

730-2066 (Base)

653.3

560

560

1

4 MB

262

730-2065 (1509)

280

240

560

1

4 MB

262

730-2065 (1508)

140

120

560

1

4 MB

262

730-2065 (1507)

81.7

70

560

1

4 MB

262

730-2065 (Base)

1225

1050

1600

4

4 MB

255

720-2064 (1505)

653.3

560

1600

4

4 MB

255

720-2064 (1504)

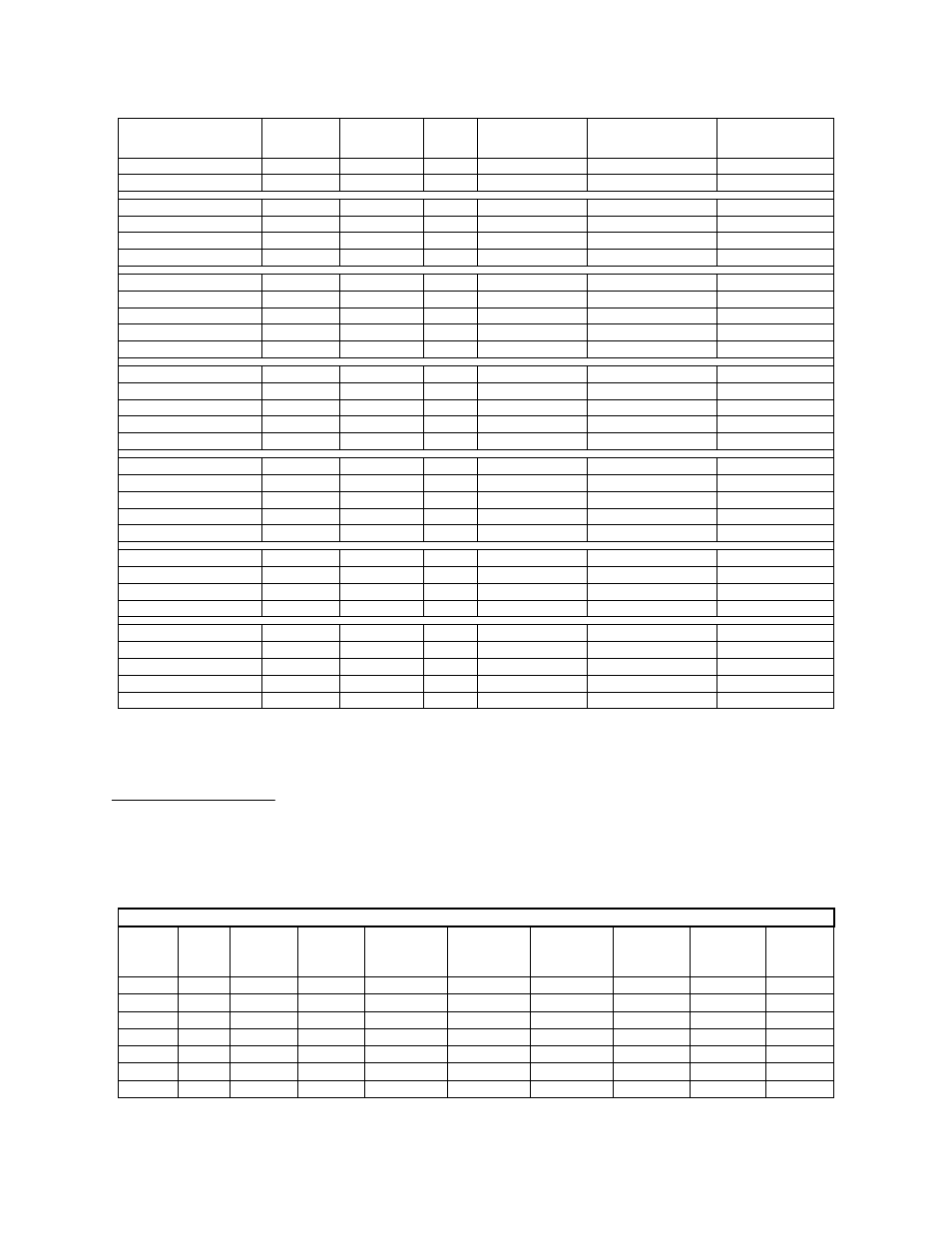

Interactive CPW

(Max)

Interactive CPW

(Knee)

Processor CPW

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

C.12.2 Model 170 Servers

Current 170 Servers

MAX Interactive CPW = Interactive CPW (Knee) * 7/6

CPU % used by Interactive @ Knee = Interactive CPW (Knee) / Processor CPW * 100

CPU % used by Processor @ Knee = 100 - CPU % used by Interactive @ Knee

CPU % used by Interactive @ Max = Max Interactive CPW / Processor CPW * 100

7.5

6.4

92.3

81.7

70

1090

4 MB

255 MHz

2

2388

17.8

15.2

84.8

81.7

70

460

4 MB

252 MHz

1

2386

12.7

10.9

89.1

58.3

50

460

4 MB

252 MHz

1

2385

15.9

13.6

86.4

35

30

220

n/a

200 MHz

1

2292

25.4

21.7

78.3

29.2

25

115

n/a

200 MHz

1

2291

32

27.4

72.6

23.3

20

73

n/a

200 MHz

1

2290

35

30

70

17.5

15

50

n/a

200 MHz

1

2289

Interactive

CPU %

@ Max

Interactive

CPU %

@ Knee

Processor

CPU %

@ Knee

Interactive

CPW

(Max)

Interactive

CPW

(Knee)

Processor

CPW

L2 cache

per CPU

Chip

Speed

CPUs

Feature #

Table C.12.2.1 Current Model 170 Servers

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

©

Copyright IBM Corp. 2008

Appendix C CPW, CIW and MCU for System i Platform

362