Epson 6200A User Manual

Page 30

24

EPSON

S1C6200/6200A CORE CPU MANUAL

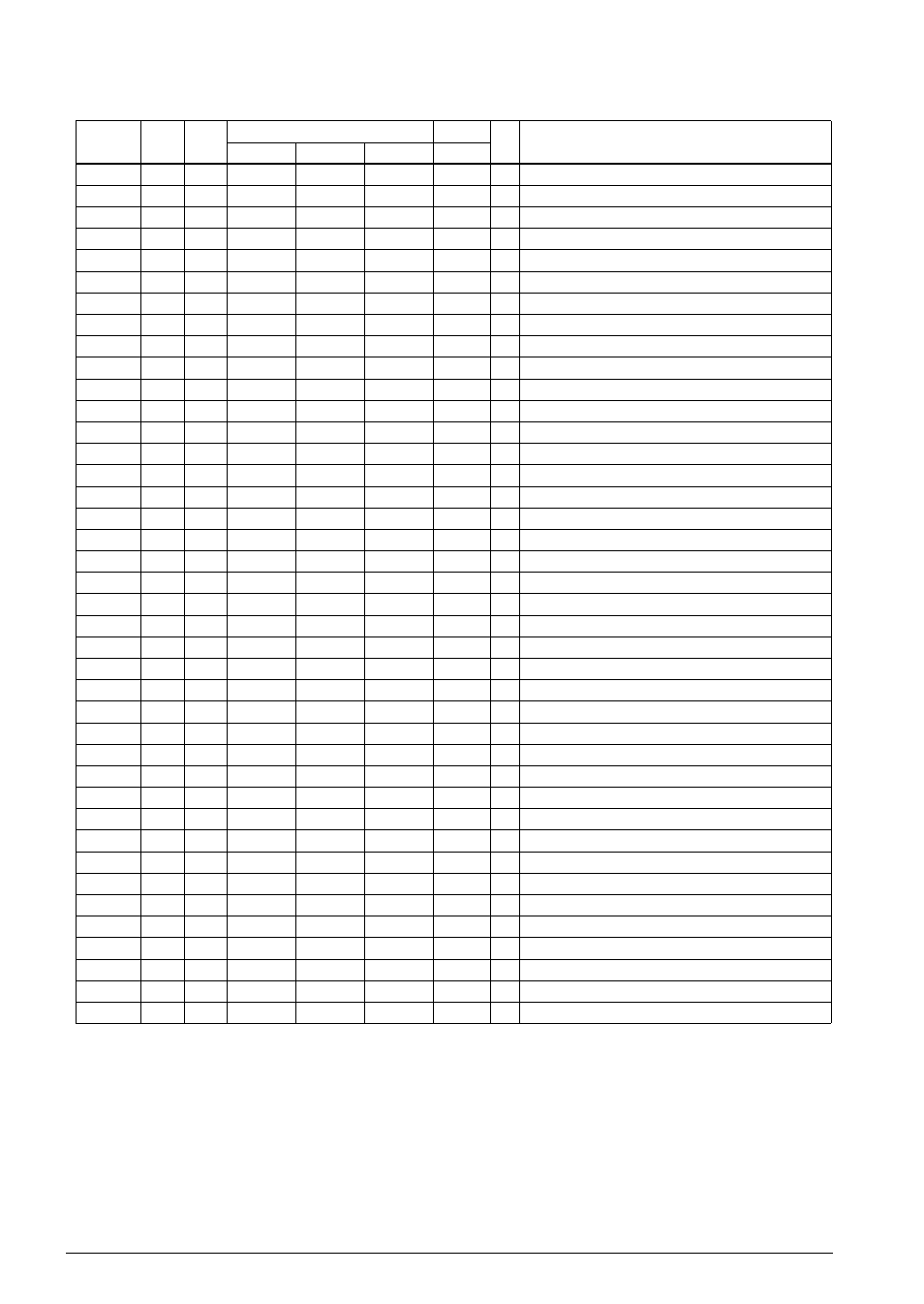

3 INSTRUCTION SET

B

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

A

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

9

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

8

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

7

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

6

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

5

0

1

1

0

0

0

0

0

0

0

1

1

1

1

1

1

0

1

1

1

1

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

1

1

0

4

p4

0

1

0

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

1

1

0

1

0

0

1

1

0

0

0

0

0

1

1

1

1

1

0

1

0

3

p3

i3

i3

0

0

1

1

0

0

1

0

0

1

0

0

1

r1

0

r1

0

r1

r1

r1

1

1

1

1

i3

0

0

0

1

i3

0

1

1

1

n3

n3

n3

2

p2

i2

i2

0

1

0

1

0

1

0

0

1

0

0

1

0

r0

0

r0

0

r0

r0

r0

0

1

0

1

i2

0

0

1

0

i2

1

0

1

1

n2

n2

n2

1

p1

i1

i1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

q1

0

q1

0

q1

q1

q1

r1

r1

r1

r1

i1

0

1

0

0

i1

1

1

0

1

n1

n1

n1

0

p0

i0

i0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

q0

0

q0

0

q0

q0

q0

r0

r0

r0

r0

i0

1

0

0

0

i0

1

1

1

0

n0

n0

n0

p

MX, i

MY, i

XP, r

XH, r

XL, r

r

YP, r

YH, r

YL, r

r, XP

r, XH

r, XL

r, YP

r, YH

r, YL

r, q

X

r, q

Y

r, q

r, q

r, q

MX, r

MY, r

MX, r

MY, r

F, i

F, i

Mn

Mn

Mn, A

PSET

LDPX

LDPY

LD

LD

LD

RRC

LD

LD

LD

LD

LD

LD

LD

LD

LD

LD

INC

LDPX

INC

LDPY

CP

FAN

ACPX

ACPY

SCPX

SCPY

SET

SCF

SZF

SDF

EI

RST

DI

RDF

RZF

RCF

INC

DEC

LD

I D Z C

↑

↑

↓

↓

★

★

★

★

↑

↑

↓

↓

↑

↑

↑

↑

↑

↑

↑

↑

↑

↓

↓

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↓

↓

↑

↑

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

5

NBP

←

p4, NPP

←

p3~p0

M(X)

←

i3~i0, X

←

X+1

M(Y)

←

i3~i0, Y

←

Y+1

XP

←

r

XH

←

r

XL

←

r

d3

←

C, d2

←

d3, d1

←

d2, d0

←

d1, C

←

d0

YP

←

r

YH

←

r

YL

←

r

r

←

XP

r

←

XH

r

←

XL

r

←

YP

r

←

YH

r

←

YL

r

←

q

X

←

X+1

r

←

q, X

←

X+1

Y

←

Y+1

r

←

q, Y

←

Y+1

r-q

r

Λ

q

M(X)

←

M(X)+r+C, X

←

X+1

M(Y)

←

M(Y)+r+C, Y

←

Y+1

M(X)

←

M(X)-r-C, X

←

X+1

M(Y)

←

M(Y)-r-C, Y

←

Y+1

F

←

F

V

i3~i0

C

←

1

Z

←

1

D

←

1 (Decimal Adjuster ON)

I

←

1 (Enables Interrupt)

F

←

F

Λ

i3~i0

I

←

0 (Disables Interrupt)

D

←

0 (Decimal Adjuster OFF)

Z

←

0

C

←

0

M(n3~n0)

←

M(n3~n0)+1

M(n3~n0)

←

M(n3~n0)-1

M(n3~n0)

←

A

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

E40 to E5F

E60 to E6F

E70 to E7F

E80 to E83

E84 to E87

E88 to E8B

E8C to E8F

E90 to E93

E94 to E97

E98 to E9B

EA0 to EA3

EA4 to EA7

EA8 to EAB

EB0 to EB3

EB4 to EB7

EB8 to EBB

EC0 to ECF

EE0

EE0 to EEF

EF0

EF0 to EFF

F00 to F0F

F10 to F1F

F28 to F2B

F2C to F2F

F38 to F3B

F3C to F3F

F40 to F4F

F41

F42

F44

F48

F50 to F5F

F57

F5B

F5D

F5E

F60 to F6F

F70 to F7F

F80 to F8F

Operand

Clock

Operation Code

Flag

Mne-

monic

Operation

Operation

Code (HEX)