Performing or on the fault circuits – Avago Technologies ACPL-339J-000E User Manual

Page 8

8

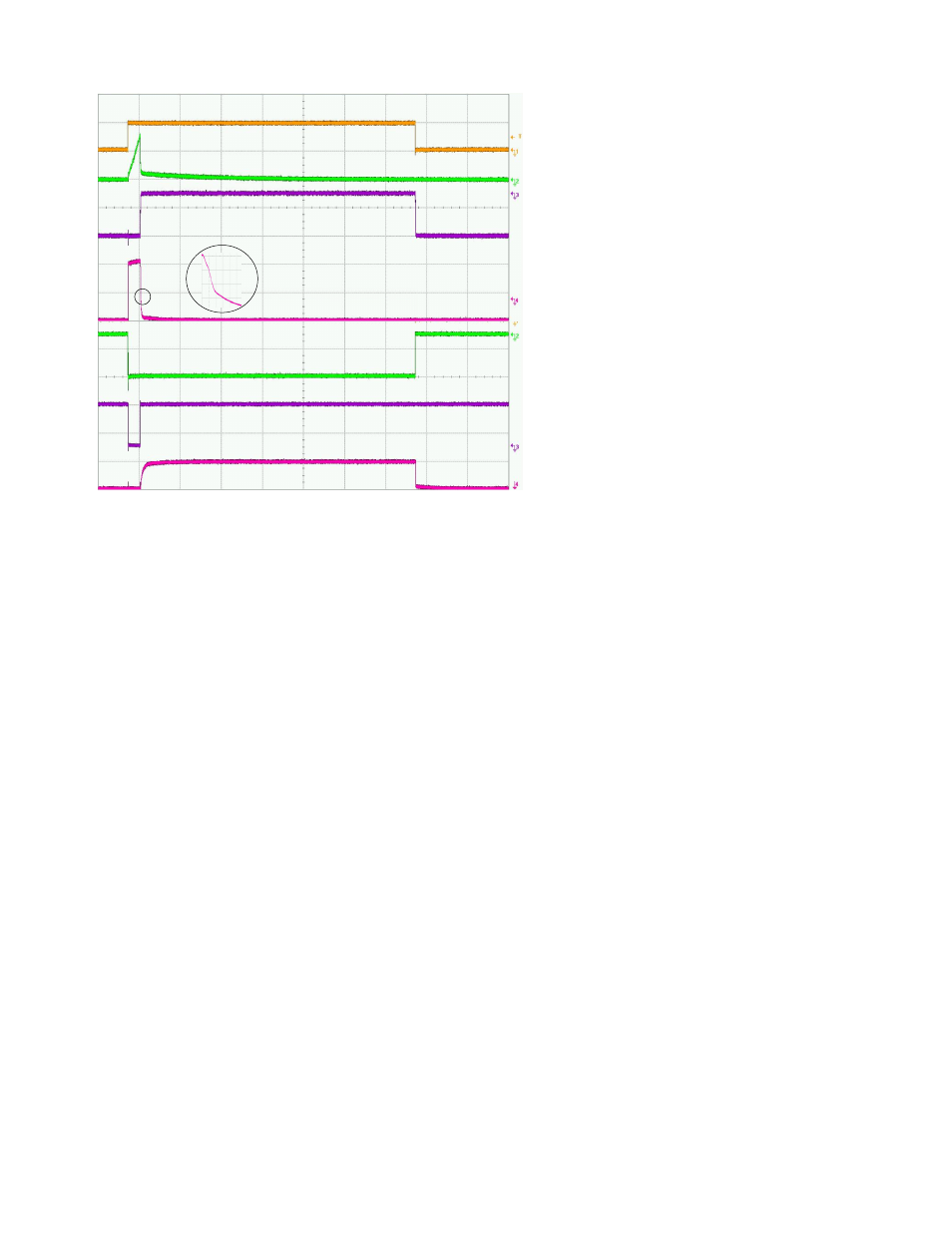

Figure 6. Input LED (t

ON

> t

MUTE

) and various output voltage waveforms

LED ON

Soft

Shutdown

I

F

V

DESAT

8 V

LED OFF

V

GMOS

V

G(IGBT)

V

OUTN

V

OUTP

FAULT

Ext NMOS OFF

Ext NMOS ON

Ext PMOS OFF

Ext PMOS ON

Figure 5 and Figure 6 also show that, once DESAT fault is detected, the output (V

gIGBT

) will be muted for T

MUTE

time

where input LED signals will be ignored during the mute period to allow for the driver to completely perform a soft

shutdown of the IGBT. The fault is auto-reset upon the 1 ms (typical) mute time (T

MUTE

) timeout or upon LED Input ‘High’

to ‘Low’ transition, whichever is later. In this way there is a minimum timeout, yet there is still flexibility of lengthening

the timeout, as in Figure 6.

Performing OR on the Fault Circuits

During normal operation of the circuit under ‘no fault’ condition, LED2 of U1 (IC1) are activated and normally ‘On’,

to pull their respective pin 7 ‘Low’. To improve on the operating efficiencies, and at the same time to allow for easy

bootstrapping, the LEDs are made to operate at 50% duty cycle at a frequency of 5 MHz through internal oscillator

circuits. This, however, causes the open collector Fault output at pin 7 of U1 to toggle at undesirable ‘High’ and ‘Low’

levels if only pull-up resistors are connected. To filter away the unwanted oscillating outputs and to keep it at a Low

level, an RC network each is connected (see Figure 7) for both ICs (IC1 and IC2) in the Top and Bottom Arms of the Half-

Bridge Inverter Drivers. Corner frequencies of both networks are set at around 15 ~ 16 kHz to have effective filtering.

During an actual fault condition, however, pin 7 will be pulled ‘High’. Due to this positive (or ‘High’) logic, the Fault pins

cannot be tied together to achieve a common Fault level if one and only one of the Inverter Arms experiences a fault.

Tying the Fault pins together causes the voltage level of both Fault pins to stay Low when only one of the ICs experiences

a fault—this is undesirable.

To overcome such a problem and to allow the circuit to correctly report a common Fault level to the microcontroller, a

circuit that performs the OR function consists of an NPN transistor and a base resistor can each be connected to the Fault

pin of their respective IC. As shown in Figure 7, the collector outputs can then be tied (perform an OR) together before a

pull-up resistor and the point on which the OR is performed represents a common Fault signal, albeit in a reversed logic.