Verilink NCC 2020 (880-503284-001) Product Manual User Manual

Page 39

Configuration

Verilink NCC 2020 User Manual

3-17

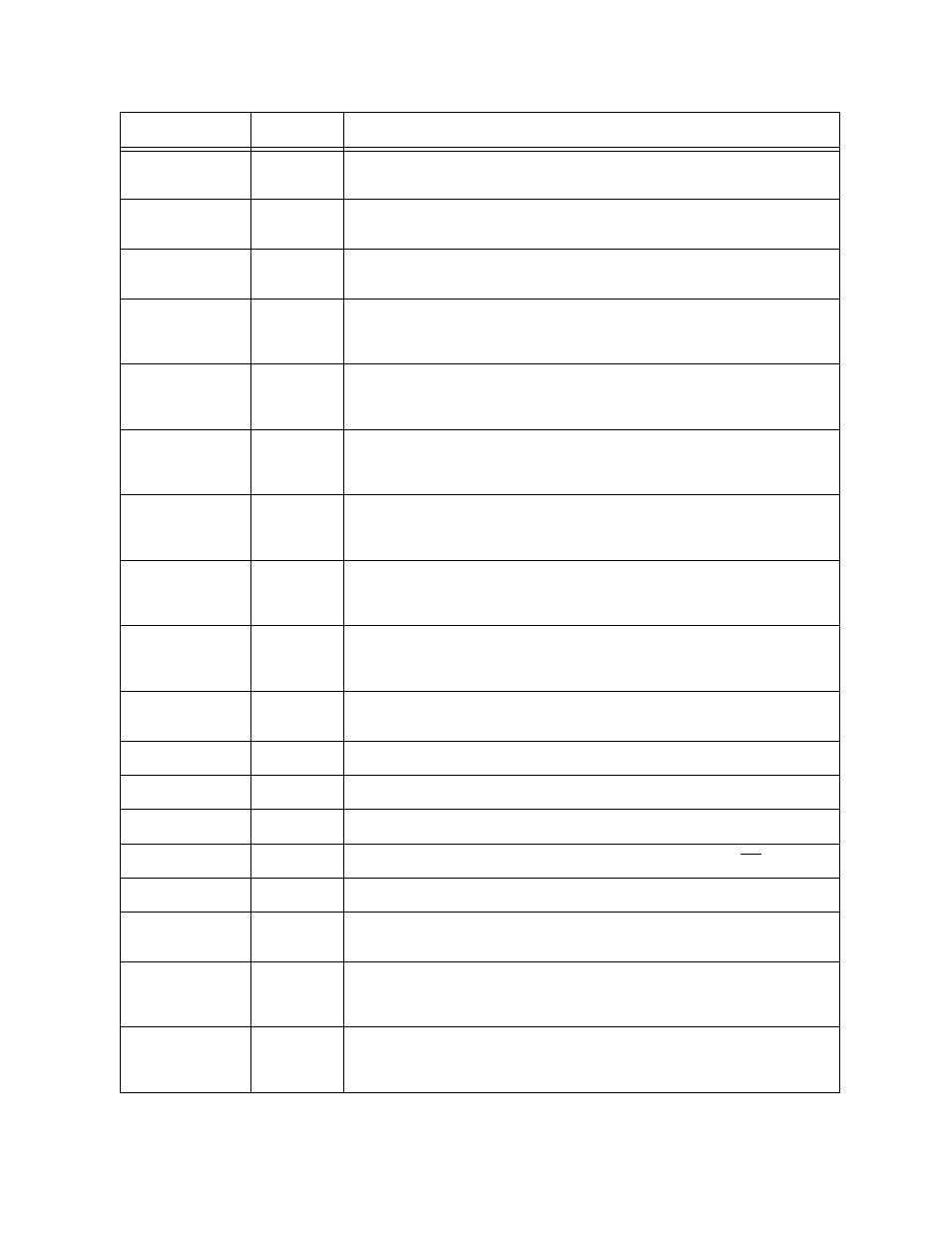

53

NCC 2020

TAC 2010

Selects DSX-1 Equipment cable length of 399-532 ft.

54

NCC 2020

TAC 2010

Selects DSX-1 Equipment cable length of 533-655 ft.

55

NCC 2020

TAC 2010

Sets data bus to NONE (CSU mode) [default].

56

NCC 2020

TAC 2010

DIU 2140

Sets data bus to A (Mux mode).

57

NCC 2020

TAC 2010

DIU 2140

Sets data bus to B (Mux mode).

58

NCC 2020

TAC 2010

DIU 2140

Sets data bus to C (Mux mode).

59

NCC 2020

TAC 2010

TAC 2130

Sends in-band CSU loop-up code to far-end CSU, this should cause the

far end CSU to enter a Line Loopback condition.

60

NCC 2020

TAC 2010

TAC 2130

Sends framed QRSS to far end.

61

NCC 2020

TAC 2010

TAC 2130

Stops QRSS pattern and send inband CSU loop-down code to far end.

62

DIU 2140

Uses timeslot 24 on the assigned CSU. Sets all 5 data ports to 9.6

kbit/s.

63

DIU 2140

Selects split timing (RX clock ~ TX clock); typical value.

64

DIU 2140

Selects single source timing (RX clock = TX clock).

65

DIU 2140

Sets DTE timing option for all synchronous data ports to ST.

66

DIU 2140

Sets DTE timing option for all synchronous data ports to ST.

67

DIU 2140

Sets DTE timing option for all synchronous data ports to TT.

68

DIU 2140

Sets RTS to normal operation. For synchronous data ports, data is

transmitted ONLY if the DTE asserts RTS (ignored in Async) [default].

69

DIU 2140

Sets RTS to forced on (requires version 1.1 DIU 2140 firmware), data is

sent regardless of actual state of RTS from DTE. This behavior always

applies to Async ports.

80

DIU 2130

TAC 2130

Sets Data Port 1 to tail-circuit timing. Note that TAC 2130-T and TAC

2130-S modules do not support tail circuit timing, external timing or

TIU 2850 timing.

Code

Applies to

Description