Outline description, Figure 3: block diagram – Sundance SMT317 User Manual

Page 7

Version 6.1

Page 7 of 24

SMT317 User Manual

4.

Outline Description

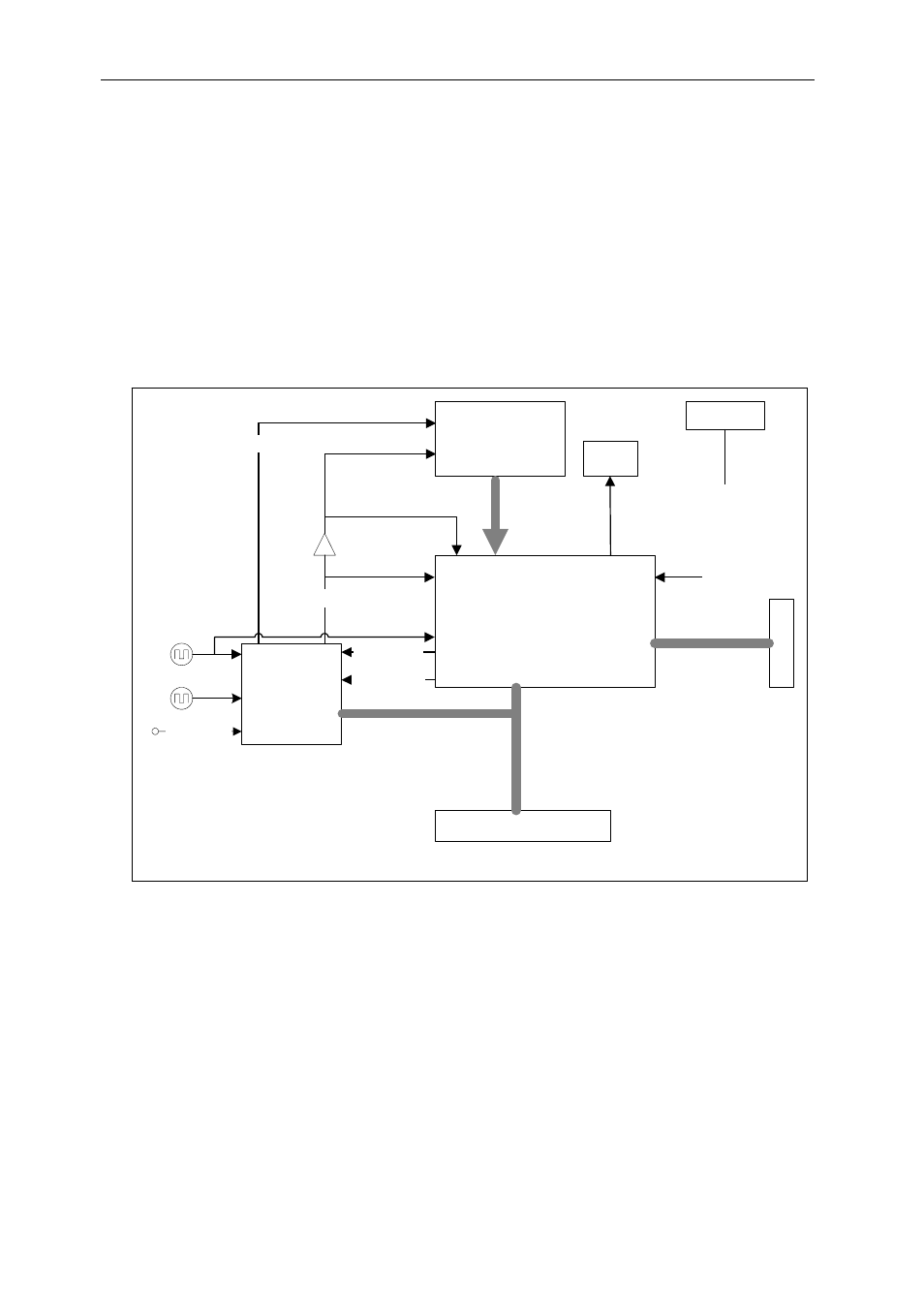

The SMT317v2 module is an ADC-based size 1 TIM offering the following features:

• Eight 16-bits ADCs running at an output word rate of up to 1.2 MHz for input

bandwidths up to 460 kHz.

• a Xilinx XCV300 Virtex FPGA.

• FPGA programming via communication port (comm-port3).

• High bandwidth data I/O via 1 Sundance Digital Bus (SDB).

VIRTEX

ADC SUB-SYSTEM

S

D

B

4 LEDs

4 I/Os

JUMPERS

CONFIG CPLD

on Comm-port3

Local clock

37.6 MHz

PRIMARY

1 SDB

Comm-port 3

External clock

Clock Buffer

Sample clock

Clock select

SYNC

External SYNC

8 A

D

C

s

Cl

ock

Co

nt

ro

l Co

mm-po

rt

s

e

le

c

tion

Internal sync

C

o

m

m

-por

t 3

Figure 3: Block Diagram

See also other documents in the category Sundance Equipment:

- SMT107 (16 pages)

- SMT6035 v.2.2 (39 pages)

- SMT6012 v.4.6 (22 pages)

- FC100 (12 pages)

- FC108 v.1.1 (10 pages)

- SMT6065 v.4.0 (45 pages)

- FFT v.2.1 (19 pages)

- SMT111 (18 pages)

- SMT118LT (10 pages)

- SMT118 (20 pages)

- SMT123-SHB (13 pages)

- SMT128 (15 pages)

- SMT145 (18 pages)

- SMT148 (35 pages)

- SMT130 v.1.0 (46 pages)

- SMT148FX (48 pages)

- SMT310Q (55 pages)

- PARS (70 pages)

- SMT166-FMC (52 pages)

- SMT166 (44 pages)

- SMT300Q v.1.6 (61 pages)

- SMT310 v.1.6 (50 pages)

- SMT326v2 (24 pages)

- SMT338 (19 pages)

- SMT349 (32 pages)

- SMT339 v.1.3 (27 pages)

- SMT338-VP (22 pages)

- SMT358 (25 pages)

- SMT351T (37 pages)

- SMT351 (25 pages)

- SMT350 (45 pages)

- SMT362 (30 pages)

- SMT365G (23 pages)

- SMT364 (37 pages)

- SMT373 (15 pages)

- SMT368 (24 pages)

- SMT370v3 (46 pages)

- SMT377 (22 pages)

- SMT381 2007 (31 pages)

- SMT381-VP (81 pages)

- SMT387 (42 pages)

- SMT391 (18 pages)

- SMT384 (47 pages)

- SMT390-VP (55 pages)