Control register description – Sundance SMT317 User Manual

Page 15

Version 6.1

Page 15 of 24

SMT317 User Manual

13.5.

Control register description

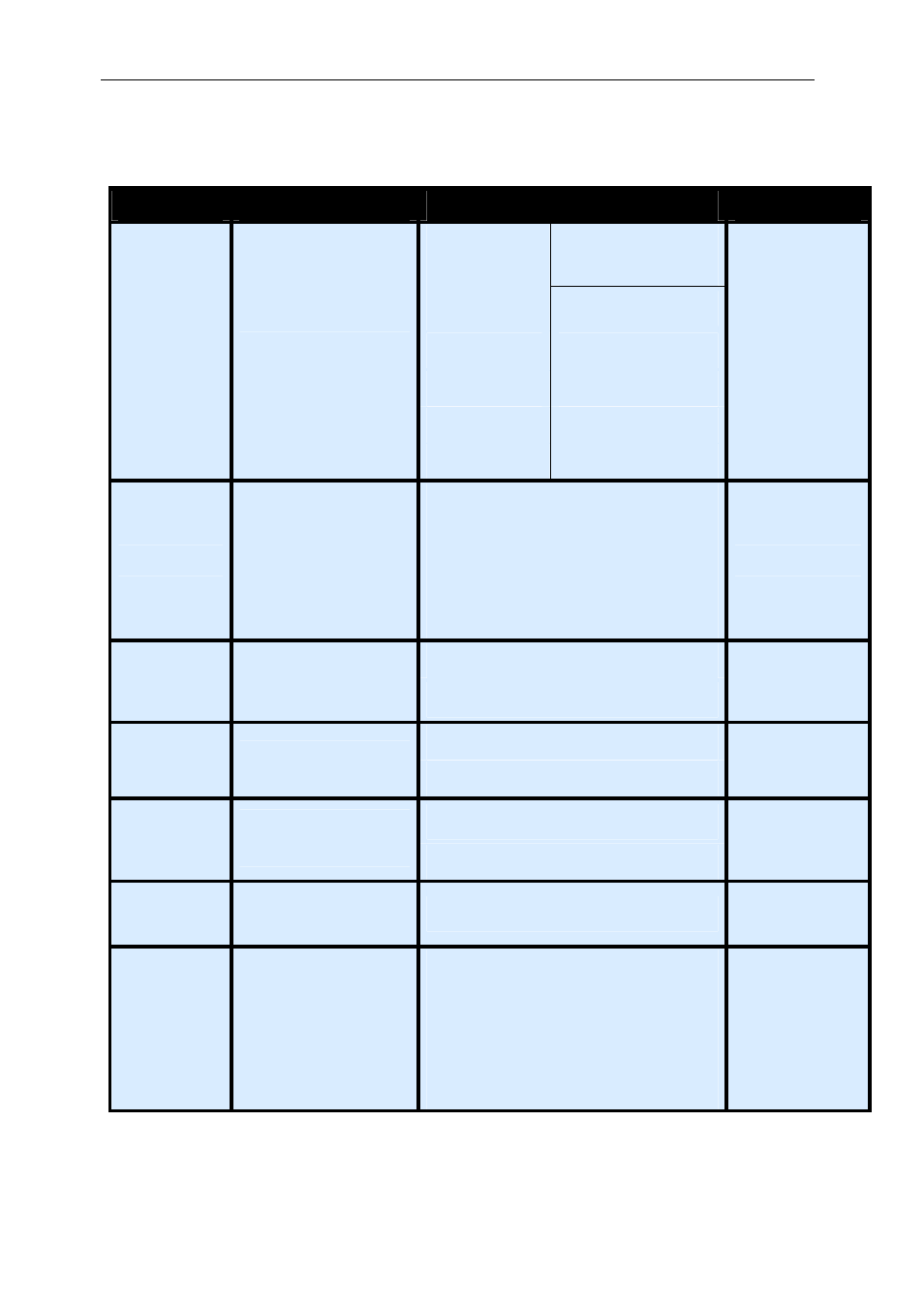

The following table describes how behave the different fields of the control register

depending on their value.

FIELD

DESCRIPTION

ACTION

DEFAULT

ADC

Clock Frequency

CLKDIV = 0

18.8 Mhz

CLKDIV = 1

9.4 Mhz

CLKDIV = 2

6.27 Mhz

CLKDIV = 3

4.7 Mhz

CLK DIV

Clock divider.

CLKDIV = 15

1.17 Mhz

CLKDIV=15

Rst_SDB

Reset FIFO

Rst_SDB = 1: Clear outgoing SDB

FIFO and send a Reset SDB for

the receiving end (Reset only valid

for SMT332/372).

Can be used to synchronise data

at the receiving end

Rst_SDB = 0

CHx = 1 enables ADC channel x

CHx

ADC Channel x

enable in outgoing

SDB FIFO.

CHx = 0 disables ADC channel x

CHx = 1

LEDx = 0 lights LEDx

LEDx

LEDx illumination.

LEDx = 1 turns LEDx off

LED[4:2]=101

EXT = 1 selects external clock

EXT Clock

Select the sampling

Clock source.

EXT = 0 selects internal clock

EXT = 0

MODE 0,

MODE 1

Parallel/Serial

interface

MODE 0 = 0

MODE 1 = 0

Internal

SYNC

Synchronisation

logic

Internal_SYNC = 1, an internal

pulse is sent to SYNC.

Internal_SYNC = 0, an external

signal is used for SYNC.

See

about SYNC function.

Internal_SYNC

= 0