Sensoray 526 User Manual

Page 9

9

determined by the state of the RTGL signal: PR0 when RTGL is low, PR1 when RTGL is high. The

autoload occurs under a programmable combination of the following conditions:

•

INDEX

↑

- rising edge of INDEX signal;

•

INDEX

↓

- falling edge of INDEX signal;

•

RO – rollover.

See application examples below for the explanation of preload registers usage.

The preload registers are 24 bits long, so they can not be written to with one operation. In order

to prevent the situation when the counter is loaded with incomplete data, an intermediate buffer

holds the high word of a preload register until the data is written to the low word, so that both

high and low words are written to the preload register simultaneously. Thus the high word has to

be always written first.

Output Register

Counter output data (24-bit) requires 2 read accesses to be read out. To ensure that all bits of

the reading correspond to the same instant each counter has an output register. The data can be

latched into the output register either by a read access to the low word of Counter Data register,

or by a hardware event, depending on the state of “Output register latch control” bit of the

Counter Mode register. The hardware event that can latch the counter data is a logical OR of any

of the following: INDEX rising edge, INDEX falling edge, interrupt timer expiration.

Latching the data into the output register does not interrupt the count. Latching on read access

occurs on the access to the low word, so in case “Latch on read” mode is selected the low word

has to be always read first.

Examples of Counter Applications

All the following examples assume the use of counter 0. The pseudocode function

RegisterWrite(address, data) has a meaning of writing a 2-byte word

data

to I/O address

(

base+address

), where

base

is the base I/O address of the board.

One-shot (software trigger)

In this mode the counter clock source is set to internal, so the length of the generated pulse

is expressed in units of 1/27 MHz

≈

37 ns. Assuming the desired positive going pulse length is

3 ms the counter has to be loaded with the value of 3 ms x 27 MHz = 81,000 = 0x13C68.

The Count Enable is set to NOT RCAP, the counter output (COUT) to RCAP with COUT polarity

inverted.

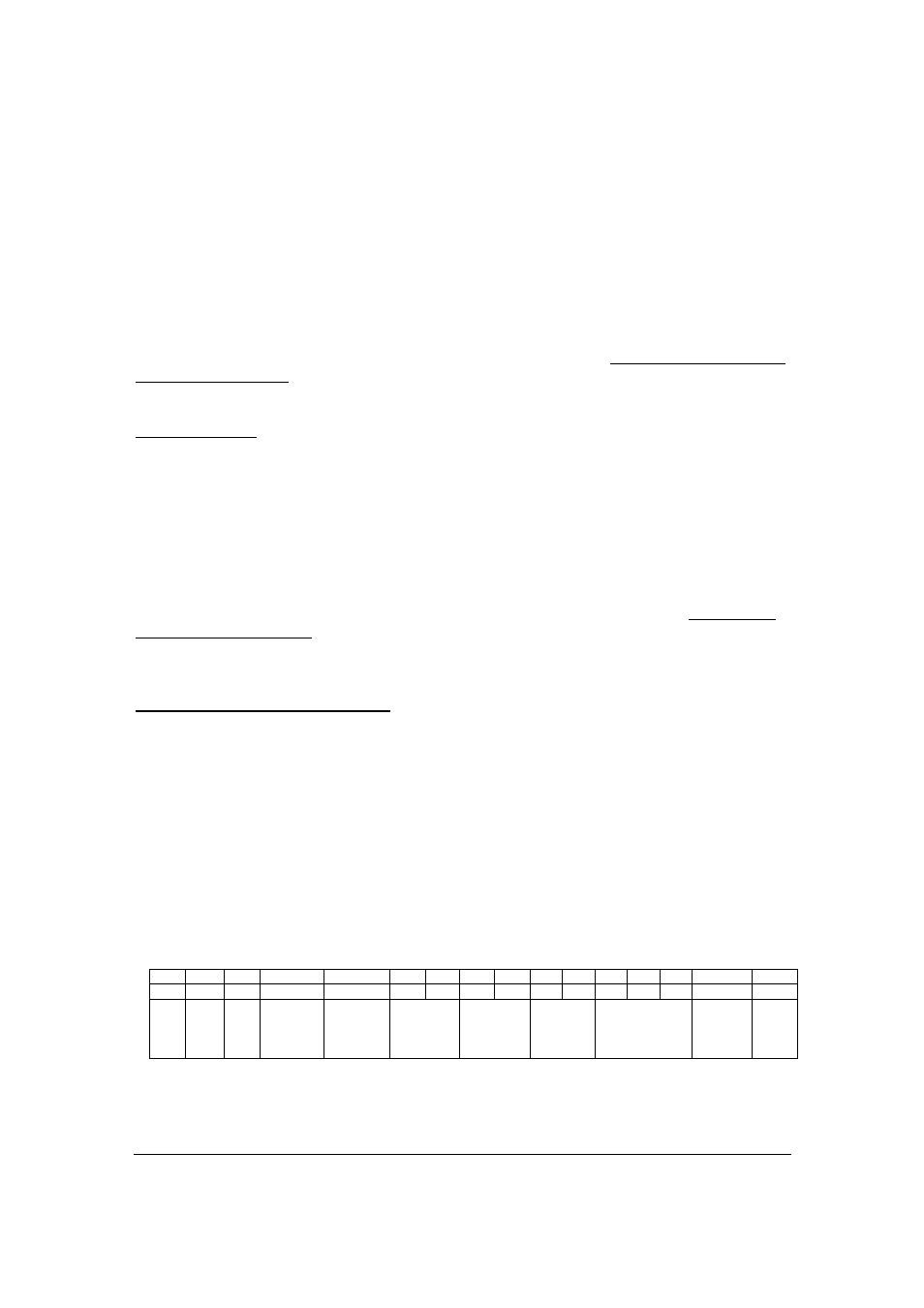

Step 1. Load the preload register PR0 with 0x13C68. First, set the Counter Mode register.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

1

1

1

0

1

0

1

1

0

0

0

1

0

X

PR0

X

Soft

count

direction

control

Count

direction:

down

Clock

source:

internal

Count

enable:

hardware

NOT

RCAP

Auto load:

disable

Polarity:

inverted

Out:

RCAP

// select PR0 as a target for Preload register access

// set operating mode, don’t enable count yet

RegisterWrite (0x16, 0x1D62); //load Counter Mode register