Registers – Sensoray 526 User Manual

Page 19

19

Registers

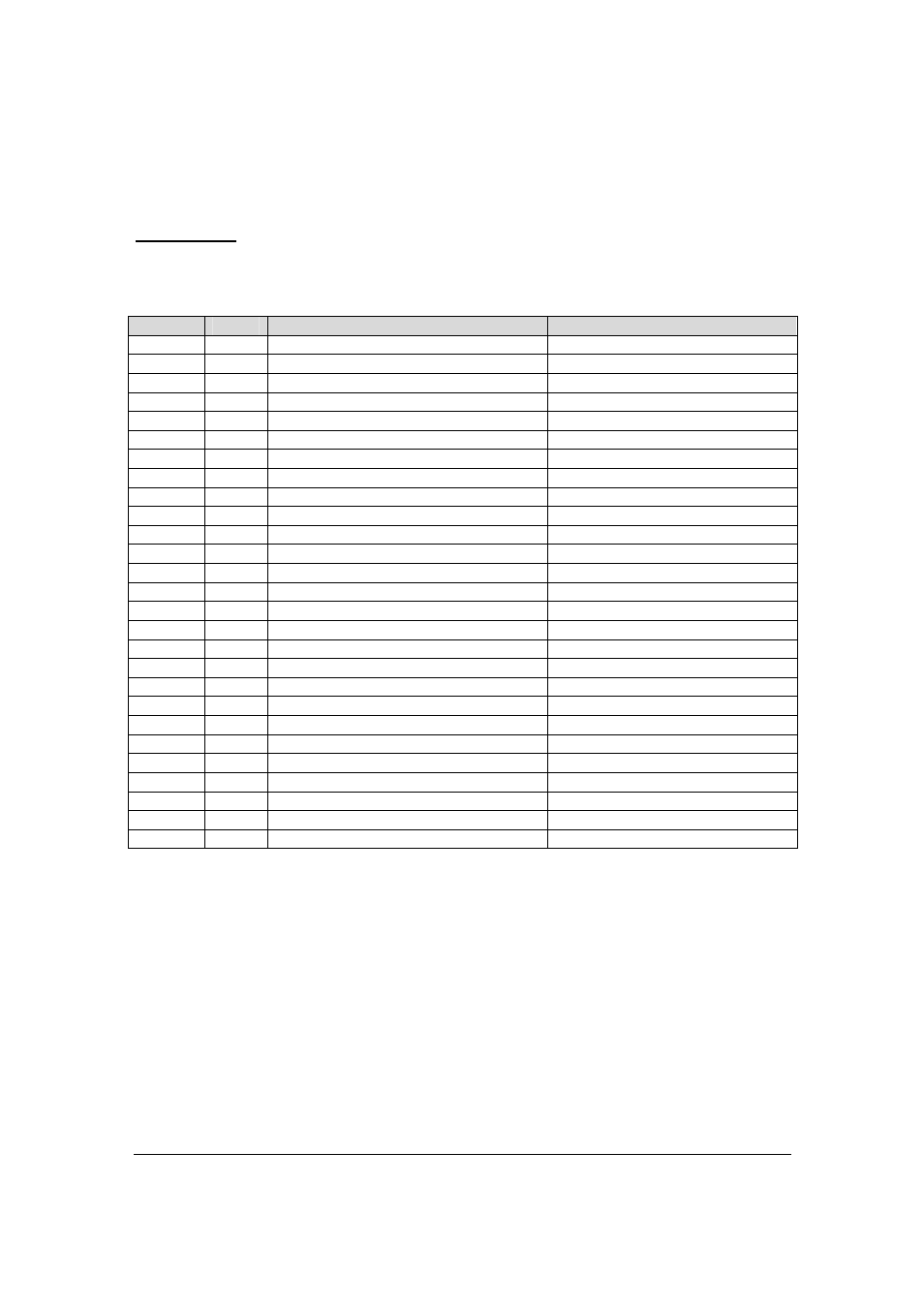

Register Map

Register addresses are relative to the base address selected with address jumpers (ADDR 15 –

6). All register accesses are 2-byte. Single byte and odd address accesses are not supported.

Address

Write

Read

0x00

TCR

Timer control register

0x02

WDC

Watchdog timer control register

0x04

DAC

DAC control

0x06

ADC

ADC control

0x08

ADD

DAC data

ADC data

0x0A

DIO

Digital I/O control

Digital I/O data

0x0C

IER

Interrupt enable register

0x0E

ISR

Interrupt status register

Interrupt status register

0x10

MSC

Miscellaneous register

Miscellaneous register

0x12

C0L

Counter 0 preload register low word

Counter 0 data low word

0x14

C0H

Counter 0 preload register high word

Counter 0 data high word

0x16

C0M

Counter 0 mode register

0x18

C0C

Counter 0 control register

Counter 0 status register

0x1A

C1L

Counter 1 preload register low word

Counter 1 data low word

0x1C

C1H

Counter 1 preload register high word

Counter 1 data high word

0x1E

C1M

Counter 1 mode register

0x20

C1C

Counter 1 control register

Counter 1 status register

0x22

C2L

Counter 2 preload register low word

Counter 2 data low word

0x24

C2H

Counter 2 preload register high word

Counter 2 data high word

0x26

C2M

Counter 2 mode register

0x28

C2C

Counter 2 control register

Counter 2 status register

0x2A

C3L

Counter 3 preload register low word

Counter 3 data low word

0x2C

C3H

Counter 3 preload register high word

Counter 3 data high word

0x2E

C3M

Counter 3 mode register

0x30

C3C

Counter 3 control register

Counter 3 status register

0x32

EED

EEPROM data

EEPROM data

0x34

EEC

EEPROM interface command

Signature

The following signal types and default values are used to specify registers implementation:

RW

read/write;

WO

write only (data read may not be the same as data written);

RR

read/reset (writing a 1 resets the corresponding bit to 0, writing a 0 has no effect);

RO

read only;

UU

unused.

0 the value after a hardware reset is 0;

1

the value after a hardware reset is 1;

X “don’t care” for write, undefined for read.