External trigger, External clock input/output – Measurement Computing E-1608-OEM User Manual

Page 23

23

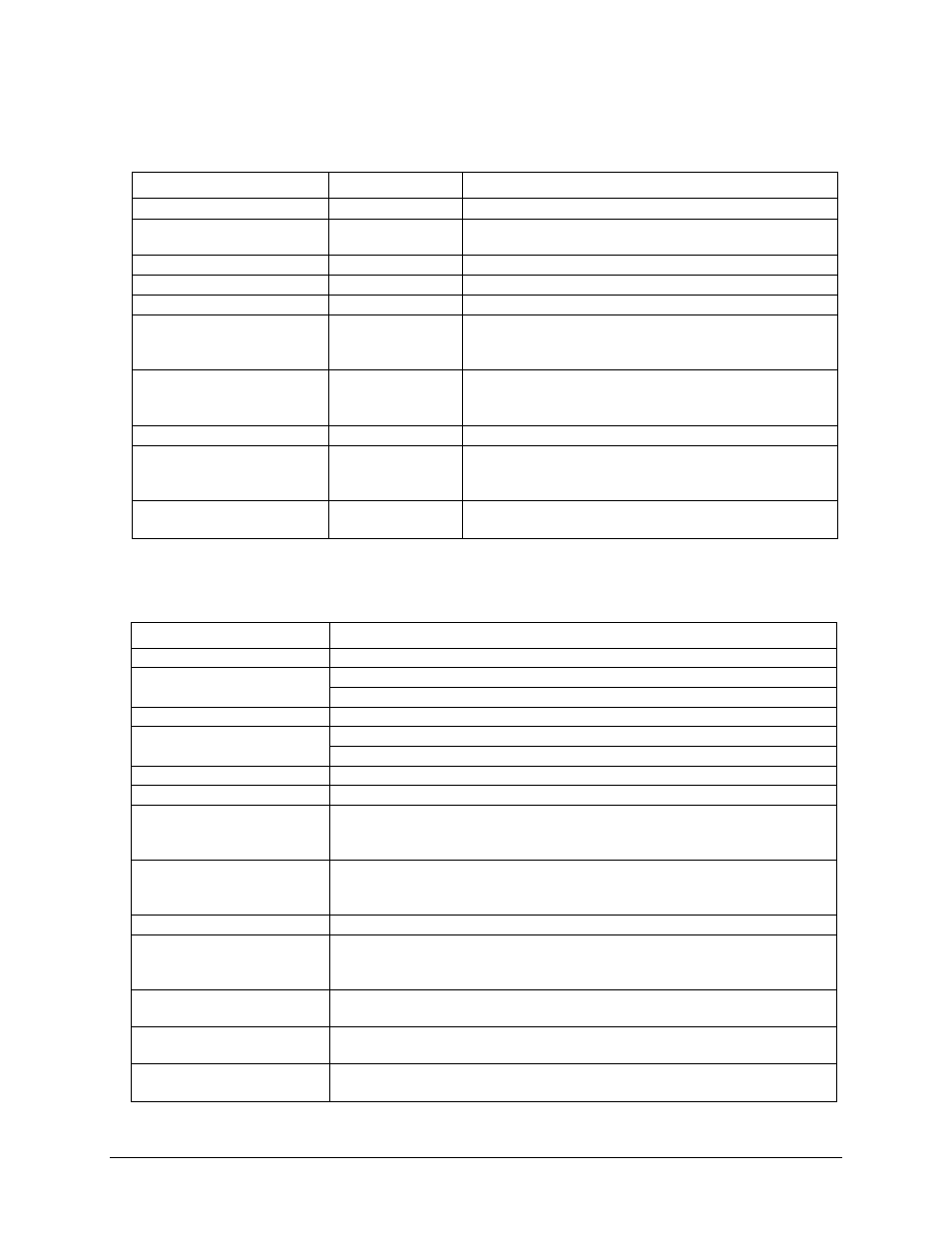

External trigger

Table 11. External trigger specifications

Parameter

Condition

Specification

Trigger source

External digital

TRIG

Trigger mode

Software-selectable

Edge or level sensitive: user configurable for CMOS

compatible rising or falling edge, high or low level.

Trigger latency

2 µs + 1 pacer clock cycle max

Trigger pulse width

1 µs min

Input type

Schmitt trigger, 47 kΩ pull-down to ground

Schmitt trigger hysteresis

1.01 V typ

0.6 V min

1.5 V max

Input high voltage threshold

2.43 V typ

1.9 V min

3.1 V max

Input high voltage limit

5.5 V absolute max

Input low voltage threshold

1.42 V typ

1.0 V min

2.0 V max

Input low voltage limit

–0.5 V absolute min

0 V recommended min

External clock input/output

Table 12. External clock I/O specifications

Parameter

Specification

Terminal names

AICKI, AICKO

Terminal types

AICKI: Input (receives A/D pacer clock from external source)

AICKO: Output (outputs internal A/D pacer clock)

Input clock rate

250 kHz max

Clock pulse width

AICKI: 1 µs min

AICKO: 1.8 µs min

Clock mode

Edge-sensitive, rising

Input type

Schmitt trigger, 47 kΩ pull-down to ground

Schmitt trigger hysteresis

1.01 V typ

0.6 V min

1.5 V max

Input high voltage threshold

2.43 V typ

1.9 V min

3.1 V max

Input high voltage limit

5.5 V absolute max

Input low voltage threshold

1.42 V typ

1.0 V min

2.0 V max

Input low voltage limit

–0.5 V absolute min

0 V recommended min

Output high voltage

4.4 V min (IOH = –50 µA)

3.80 V min (IOH = –8 mA)

Output low voltage

0.1 V max (IOL = 50 µA)

0.44 V max (IOL = 8 mA)