Advanced chipset features, Bios setup – DFI EL339-B User Manual

Page 62

62

3

BIOS Setup

Advanced Chipset Features

This section gives you functions to configure the system based on the specific

features of the chipset. The chipset manages bus speeds and access to system

memory resources.

These items should not be altered unless necessary.

The

default settings have been chosen because they provide the best operating con-

ditions for your system. The only time you might consider making any changes

would be if you discovered some incompatibility or that data was being lost while

using your system.

System BIOS Cacheable

When this field is enabled, accesses to the system BIOS ROM addressed at

F0000H-FFFFFH are cached, provided that the cache controller is enabled. The

larger the range of the Cache RAM, the higher the efficiency of the system.

Memory Hole At 15M-16M

In order to improve system performance, certain space in memory can be re-

served for ISA cards. This memory must be mapped into the memory space

below 16MB. When enabled, the CPU assumes the 15-16MB memory range is

allocated to the hidden ISA address range instead of the actual system DRAM.

When disabled, the CPU assumes the 15-16MB address range actually contains

DRAM memory. If more than 16MB of system memory is installed, this field must

be disabled to provide contiguous system memory.

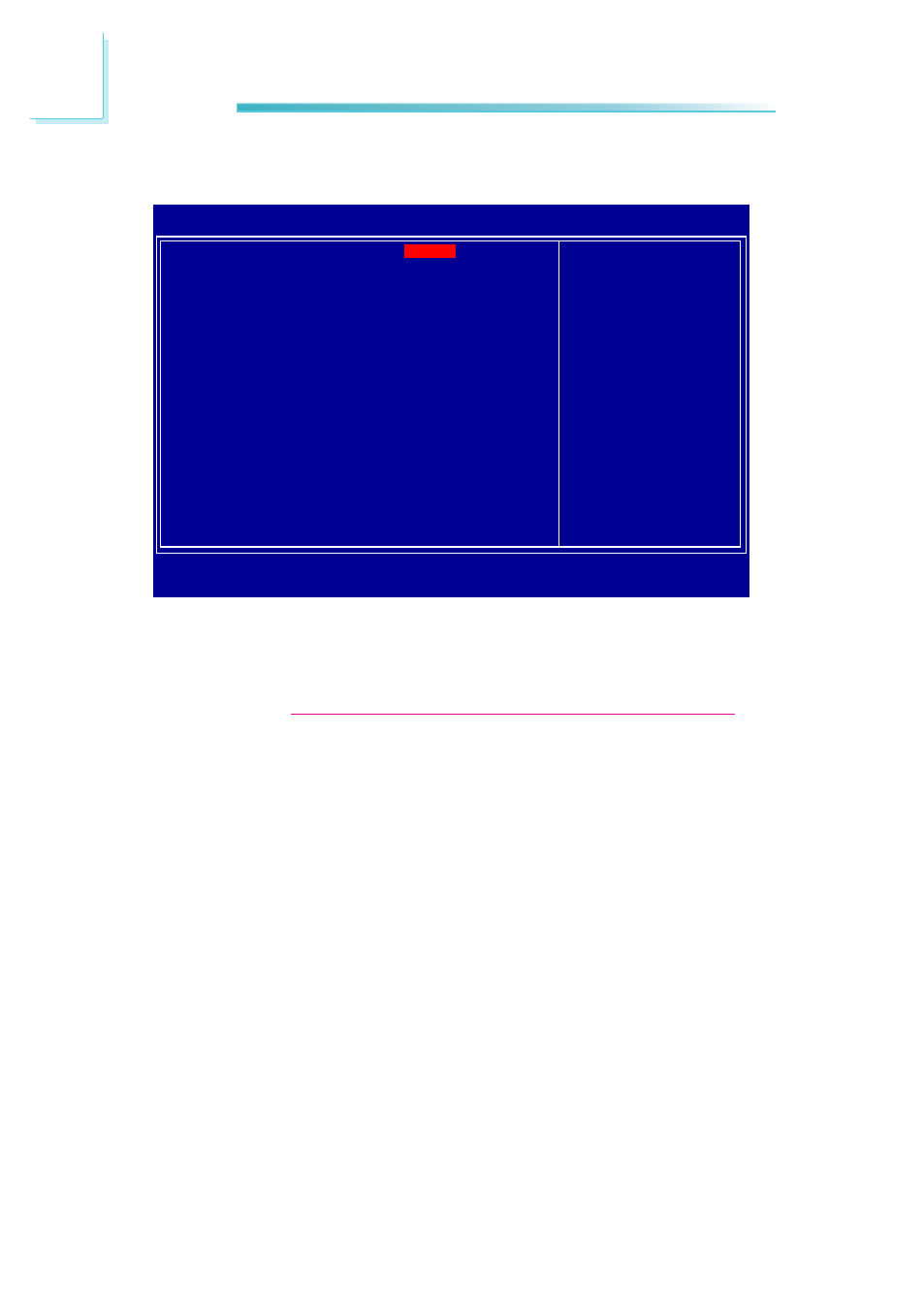

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

System BIOS Cacheable

Memory Hole At 15M-16M

PCI Express Root Port Func

** VGA Setting **

PEG/Onchip VGA Control

On-Chip Frame Buffer Size

Total GFX Memory

Item Help

Menu Level

Enabled

Disabled

Press Enter

Auto

32MB

128MB

↑↓→←

: Move

Enter: Select

F1: General Help

+/-/PU/PD: Value

F10: Save

ESC: Exit

F5: Previous Values

F6: Fail-Safe Defaults

F7: Optimized Defaults

The settings on the screen are for reference only. Your version may not be identical to

this one.