2 rp1 connector, Table 3-2, Rp1 connector pinout – Artesyn iVPX7225 RTM Installation and Use (April 2015) User Manual

Page 36: Controls, leds and connectors

Controls, LEDs and Connectors

iVPX7225 RTM Installation and Use (6806800S35B)

36

3.4.2

RP1 Connector

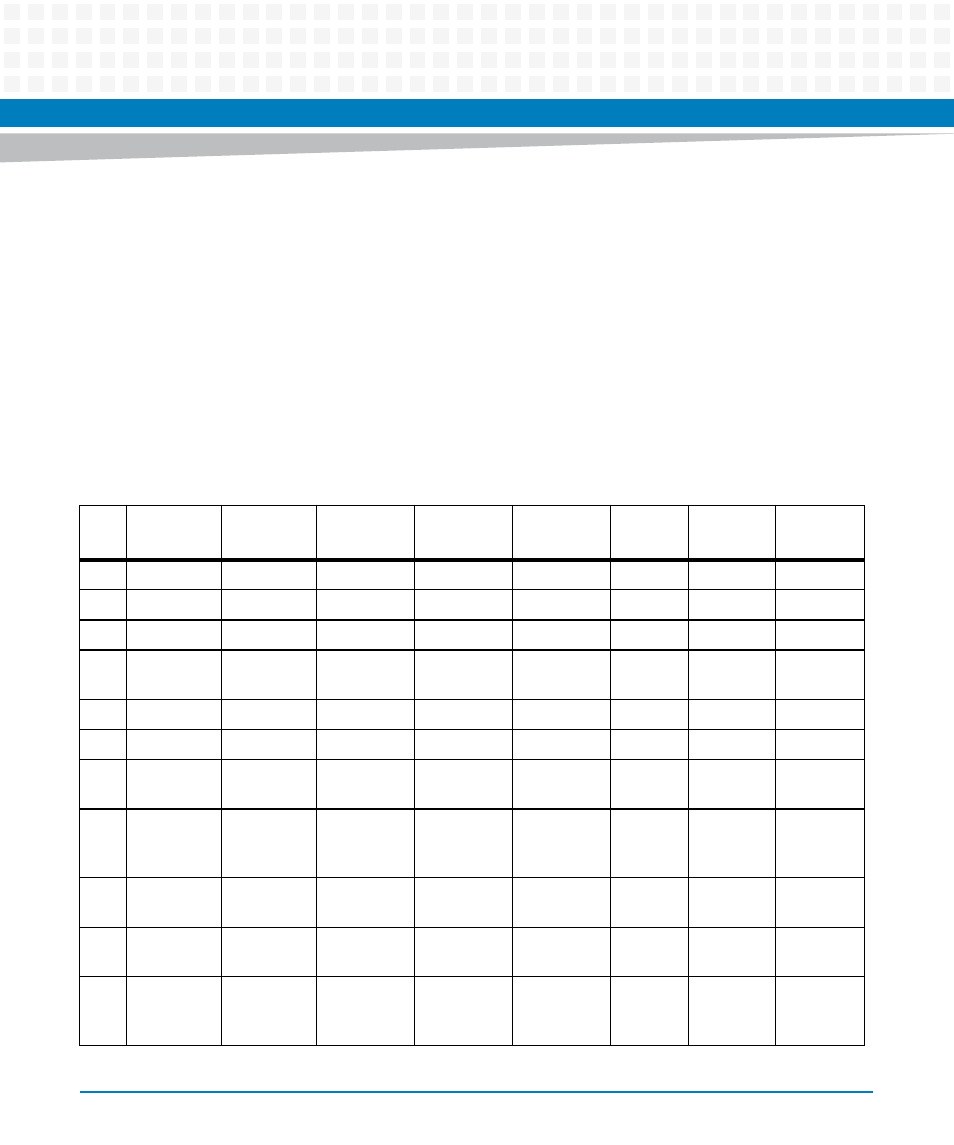

The following table provides the pinout of the RP1 connector.

1. The iVPX7225 PCH supports a battery-backed real-time clock with 256 bytes of battery-backed RAM. The PCH maintains the time

of the day and stores system data as long as the VBAT input remains above 2V (at the iVPX7225 PCH RTC input). In the event that the

system does not provide a voltage at VBAT, there is a diode protected 0.2F SuperCap (C214) onboard the iVPX7225 RTM to maintain

operation for short down times. The steady state current draw from the iVPX7225 at VBAT is 6 uA. In the event that VBAT is connected

to 3.3V_AUX at the backplane, the RTM SuperCap will discharge more quickly when 3.3V_AUX is removed. This is due to (SYSRESET)

terminations present on the VPX backplane. This could result in the loss of RTC and/or system data stored in the iVPX7225 PCH

battery-backed RAM. Refer to VITA 46 for additional information on the VBAT bussed signal.

Table 3-2 RP1 Connector Pinout

Pin

Wafer Type Row G

Row F

Row E

Row D

Row C

Row B

Row A

1

Differential CRT BLUE

GND

CRT HSYNC

CRT VSYNC

GND

CRT_CLK

CRT DATA

2

Differential GND

CRT GREEN

CRT RED

GND

USB 0 N

USB0 P

GND

3

Differential IPMC1 SCL

GND

USB1 N

USB1 P

GND

USB2 N

USB2 P

4

Differential GND

USB PEN

Reserved

GND

USB 2

PEN

USB OCP L GND

5

Differential IPMC1 SDA GND

GPIO 0

GPIO 1

GND

GPIO 2

GPIO 3

6

Differential GND

GPIO 4

GPIO 5

GND

GPIO 6

GPIO 7

GND

7

Differential NC

GND

ETH

LANE

1

TX N

ETH LANE 1

TX P

GND ETH

LANE

1 RX N

ETH LANE

1 RX P

8

Differential GND

ETH

LANE

0

TX N

ETH LANE 0

TX P

GND ETH

LANE 0

RX N

ETH LANE

0 RX P

GND

9

Differential SPI WP OR

L

GND COM0

RX

CTS N

COM0 RX

CTS P

GND COM0

TX

RTS N

COM TX

RTS P

10

Differential GND

COM1

RTS

TX N

COM1 TX P

GND

COM1

RX N

COM1 RX

CTS P

GND

11

Differential IPMC

WP

OR L

GND ETH

WP

OR

L

PCIE SW

WP OR L

GND IPMC

DEBUG

RXD

IPMC

DEBUG

TXD