Appendix a: watchdog timer – NEXCOM NDiS M533 User Manual

Page 65

Copyright © 2013 NEXCOM International Co., Ltd. All Rights Reserved.

51

NDiS M533 User Manual

Appendix A: Watchdog Timer

Appendix A: Watchdog Timer

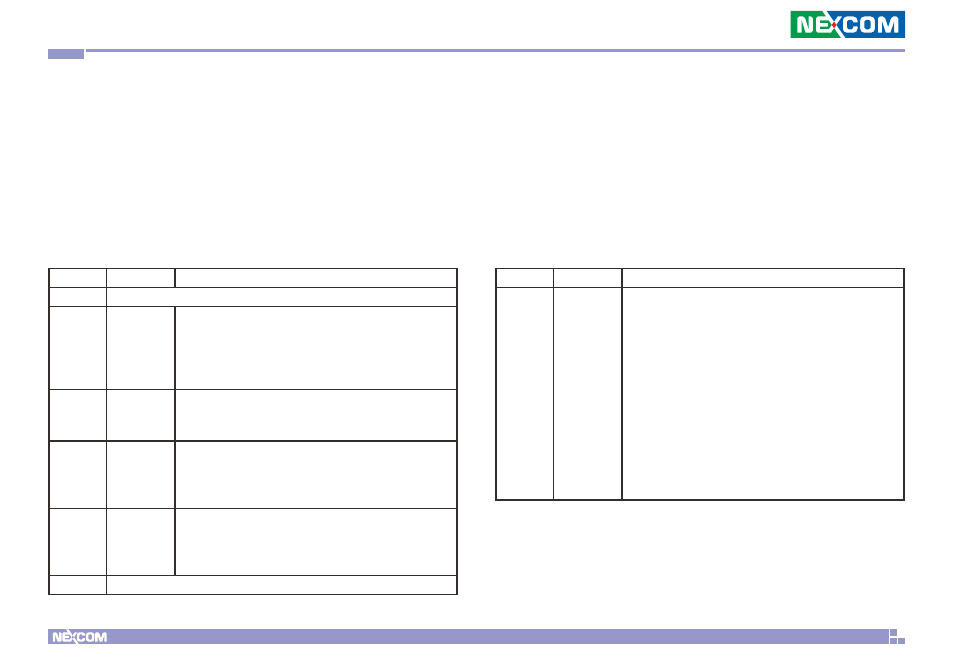

CR F0h. Watchdog Timer I(WDT1) and KBC P20 Control Mode Register

Location: Address F0h

Attribute: Read/Write

Power Well: VCC

Reset by: LRESET# or PWROK

Default: 00h

Size: 8 bits

Bit

Read/Write

Description

7-5

Reserved.

4

R / W

Watchdog Timer I count mode is 1000 times faster.

0: Disable.

1: Enable.

(If bit-3 is 0, the count mode is 1/1000 seconds mode.)

(If bit-3 is 1, the count mode is 1/1000 minutes mode.)

3

R / W

Select Watchdog Timer I count mode.

0: Second Mode.

1: Minute Mode.

2

R / W

Enable the rising edge of a KBC reset (P20) to issue a time-

out event.

0: Disable.

1: Enable.

1

R / W

Disable / Enable the Watchdog Timer I output low pulse to

the KBRST# pin (PIN59)

0: Disable.

1: Enable.

0

Reversed

CR F1h. Watchdog Timer I(WDT1) Counter Register

Location: Address F1h

Attribute: Read/Write

Power Well: VCC

Reset by: LRESET# or PWROK

Default: 04h

Size: 8 bits

Bit

Read/Write

Description

7-0

R / W

Watch Dog Timer I Time-out value. Writing a non-zero value

to this register causes the counter to load the value into the

Watch Dog Counter and start counting down. If CR F2h, bits

7 and 6 are set, any Mouse Interrupt or Keyboard Interrupt

event causes the previously-loaded, non-zero value to be

reloaded to the Watch Dog Counter and the count down

resumes. Reading this register returns the current value in

the Watch Dog Counter, not the Watch Dog Timer Time-

out value.

00h: Time-out Disable

01h: Time-out occurs after 5.03x10

7

CLKIN cycle time, by

analogy.

(5.03x10

7

x (1/48MHz) = 1.046s)