External digital trigger, Figure 3-4 – ADLINK PXIe-9848 User Manual

Page 29

Operations

19

PXIe-9848

External Digital Trigger

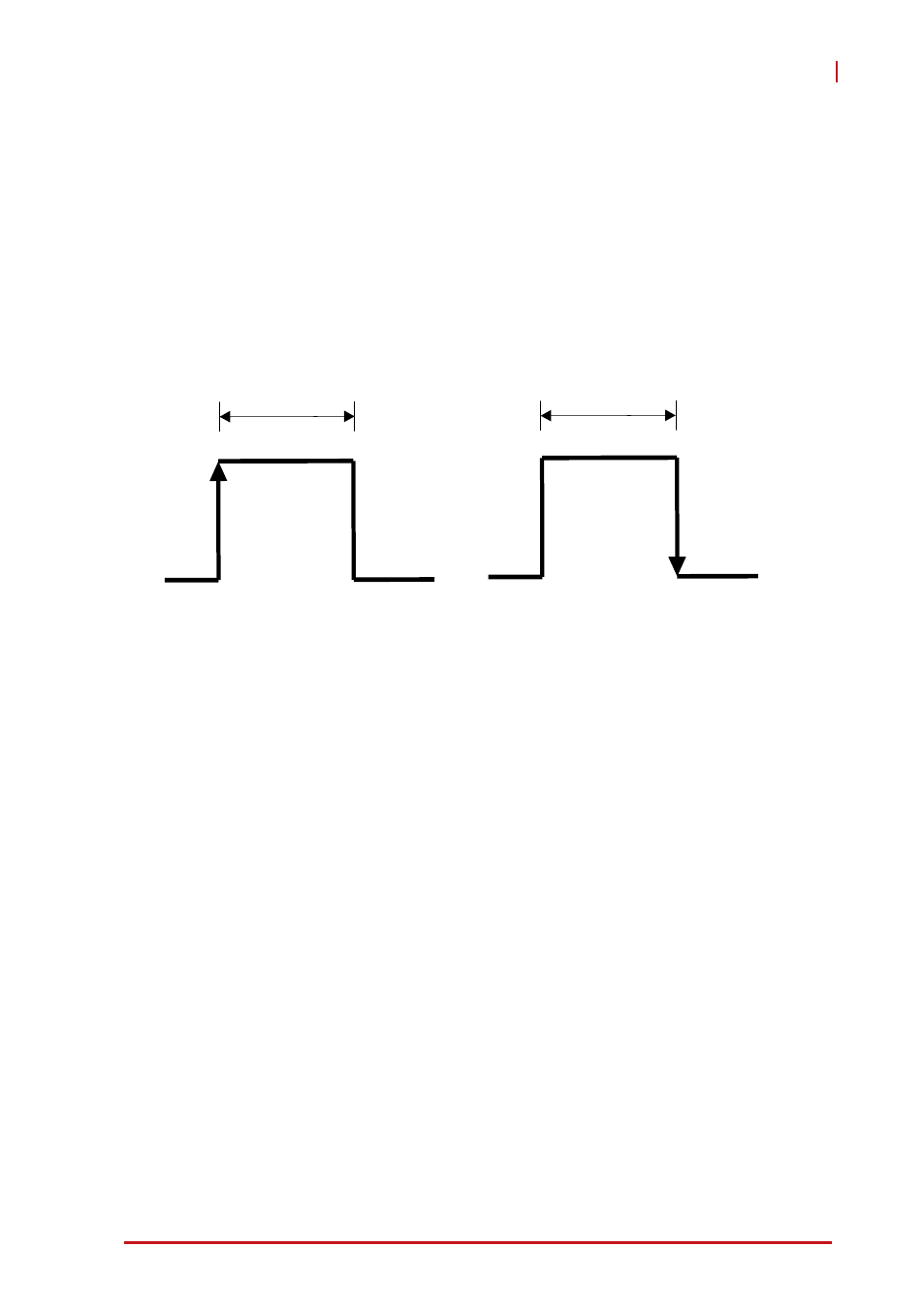

An external digital trigger is generated when a TTL edge or equiv-

alent wave slope is detected at the SMB connector on the front

panel. As shown, trigger polarity can be selected by software.

Note that minimum TTL pulse width is 20 ns and maximum input

wave frequency is 25 MHz.

Figure 3-4: External Digital Trigger

Signal level of the external digital trigger signal can be configured

by onboard potentiometer as follows. The adjustable range is

0.8mV to 3.3V and the adjustable step 0.8mV (3.3V with 12bit res-

olution). The default voltage level is 1.67V.

Pulse Width > 20ns

Pulse Width > 20ns

Rising Edge Trigger Event

Falling Edge Trigger Event

See also other documents in the category ADLINK Hardware:

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)