Cypress CY7C1223H User Manual

Page 6

CY7C1223H

Document #: 38-05674 Rev. *B

Page 6 of 16

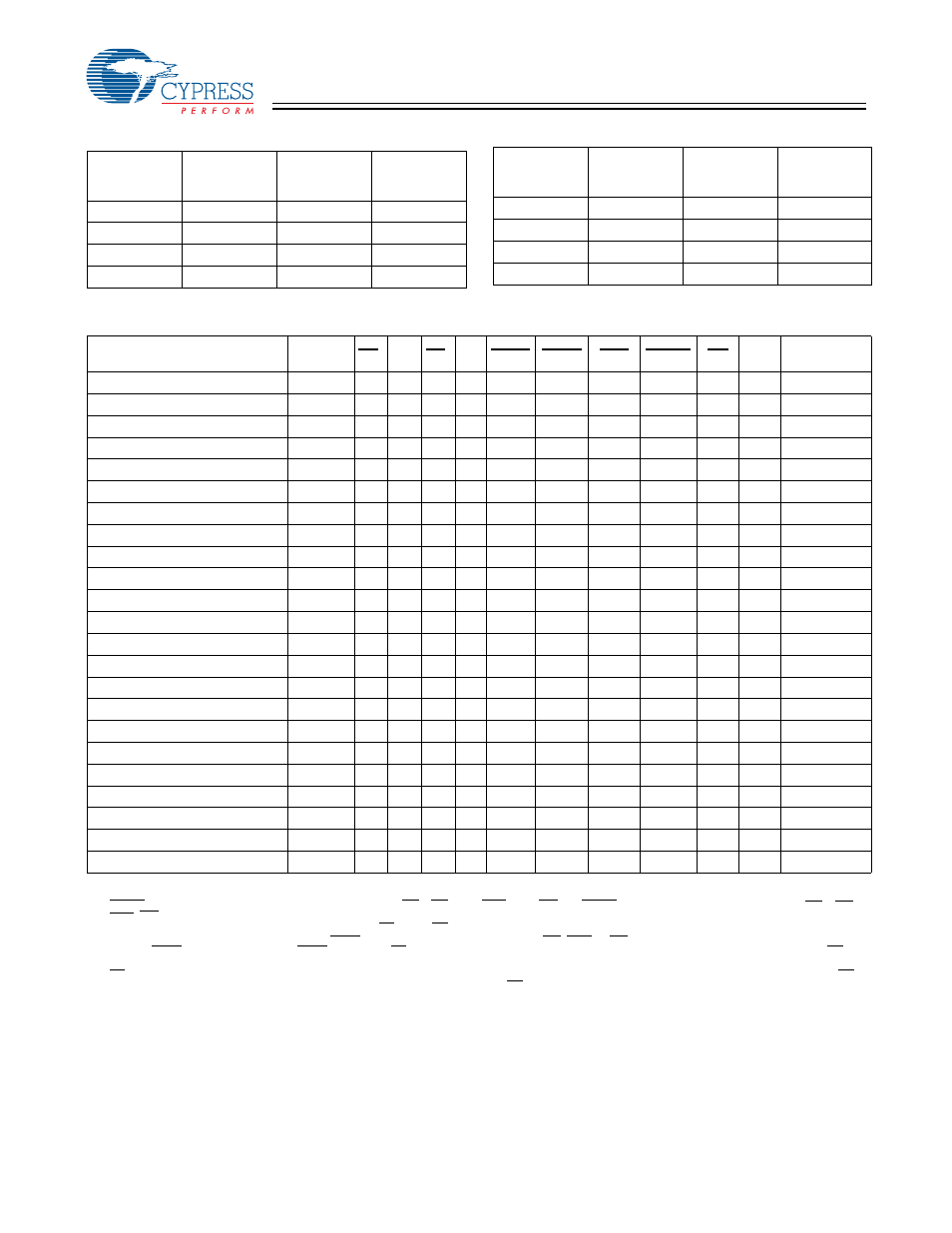

Interleaved Burst Address Table (MODE = Floating or V

DD

)

First

Address

A1, A0

Second

Address

A1, A0

Third

Address

A1, A0

Fourth

Address

A1, A0

00

01

10

11

01

00

11

10

10

11

00

01

11

10

01

00

Linear Burst Address Table (MODE = GND)

First

Address

A1, A0

Second

Address

A1, A0

Third

Address

A1, A0

Fourth

Address

A1, A0

00

01

10

11

01

10

11

00

10

11

00

01

11

00

01

10

Truth Table

[2, 3, 4, 5, 6]

Operation

Address

Used

CE

1

CE

2

CE

3

ZZ ADSP ADSC

ADV

WRITE

OE

CLK

DQ

Deselected Cycle, Power-down

None

H

X

X

L

X

L

X

X

X

L-H

Tri-State

Deselected Cycle, Power-down

None

L

L

X

L

L

X

X

X

X

L-H

Tri-State

Deselected Cycle, Power-down

None

L

X

H

L

L

X

X

X

X

L-H

Tri-State

Deselected Cycle, Power-down

None

L

L

X

L

H

L

X

X

X

L-H

Tri-State

Deselected Cycle, Power-down

None

L

X

H

L

H

L

X

X

X

L-H

Tri-State

ZZ Mode, Power-down

None

X

X

X

H

X

X

X

X

X

X

Tri-State

Read Cycle, Begin Burst

External

L

H

L

L

L

X

X

X

L

L-H

Q

Read Cycle, Begin Burst

External

L

H

L

L

L

X

X

X

H

L-H

Tri-State

Write Cycle, Begin Burst

External

L

H

L

L

H

L

X

L

X

L-H

D

Read Cycle, Begin Burst

External

L

H

L

L

H

L

X

H

L

L-H

Q

Read Cycle, Begin Burst

External

L

H

L

L

H

L

X

H

H

L-H

Tri-State

Read Cycle, Continue Burst

Next

X

X

X

L

H

H

L

H

L

L-H

Q

Read Cycle, Continue Burst

Next

X

X

X

L

H

H

L

H

H

L-H

Tri-State

Read Cycle, Continue Burst

Next

H

X

X

L

X

H

L

H

L

L-H

Q

Read Cycle, Continue Burst

Next

H

X

X

L

X

H

L

H

H

L-H

Tri-State

Write Cycle, Continue Burst

Next

X

X

X

L

H

H

L

L

X

L-H

D

Write Cycle, Continue Burst

Next

H

X

X

L

X

H

L

L

X

L-H

D

Read Cycle, Suspend Burst

Current

X

X

X

L

H

H

H

H

L

L-H

Q

Read Cycle, Suspend Burst

Current

X

X

X

L

H

H

H

H

H

L-H

Tri-State

Read Cycle, Suspend Burst

Current

H

X

X

L

X

H

H

H

L

L-H

Q

Read Cycle, Suspend Burst

Current

H

X

X

L

X

H

H

H

H

L-H

Tri-State

Write Cycle, Suspend Burst

Current

X

X

X

L

H

H

H

L

X

L-H

D

Write Cycle, Suspend Burst

Current

H

X

X

L

X

H

H

L

X

L-H

D

Notes:

2. X = “Don't Care.” H = Logic HIGH, L = Logic LOW.

3. WRITE = L when any one or more Byte Write enable signals (BW

A

, BW

B

) and BWE = L or GW = L. WRITE = H when all Byte write enable signals (BW

A

, BW

B

),

BWE, GW=H.

4. The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

5. The SRAM always initiates a read cycle when ADSP is asserted, regardless of the state of GW, BWE, or BW

[A:B]

. Writes may occur only on subsequent clocks

after the ADSP or with the assertion of ADSC. As a result, OE must be driven HIGH prior to the start of the write cycle to allow the outputs to tri-state. OE is a

don't care for the remainder of the write cycle.

6. OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle all data bits are tri-state when OE is

inactive or when the device is deselected, and all data bits behave as output when OE is active (LOW).