Cypress CY7C1223H User Manual

Page 16

CY7C1223H

Document #: 38-05674 Rev. *B

Page 16 of 16

Document History Page

Document Title: CY7C1223H 2-Mbit (128K x 18) Pipelined DCD Sync SRAM

Document Number: 38-05674

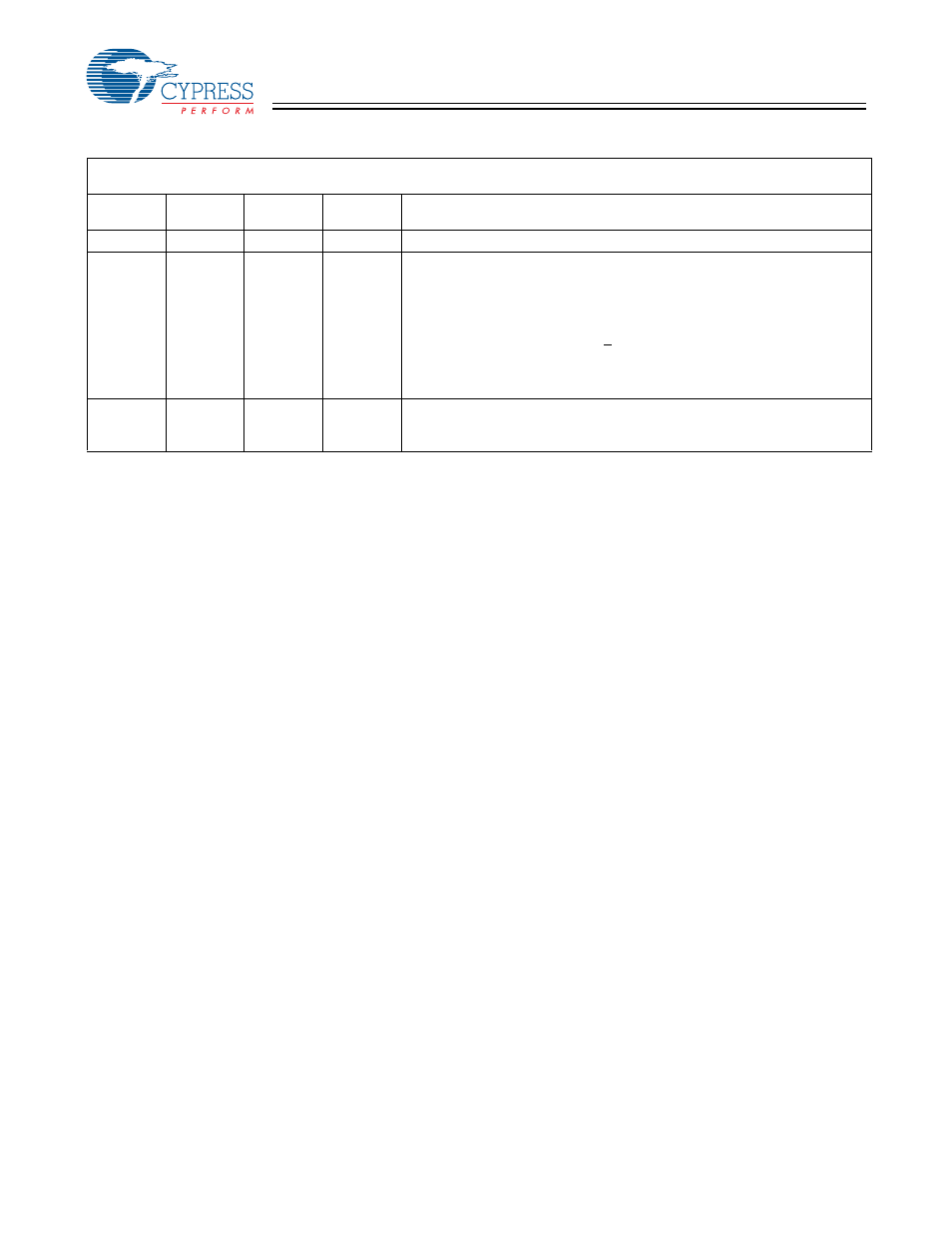

REV.

ECN NO.

Issue Date

Orig. of

Change

Description of Change

**

347357

See ECN

PCI

New Data Sheet

*A

424820

See ECN

RXU

Changed address of Cypress Semiconductor Corporation on Page# 1 from

“3901 North First Street” to “198 Champion Court”

Changed Three-State to Tri-State.

Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the

Electrical Characteristics Table.

Modified test condition from V

IH

< V

DD

to

V

IH

< V

DD

Replaced Package Name column with Package Diagram in the Ordering

Information table.

Replaced Package Diagram of 51-85050 from *A to *B

*B

459347

See ECN

NXR

Converted from Preliminary to Final

Included 2.5V I/O option

Updated the Ordering Information table.

- CY7C1410AV18 (29 pages)

- CY7C1411JV18 (28 pages)

- CY7C1383FV25 (28 pages)

- CY14B256L (18 pages)

- CY7C1307BV25 (21 pages)

- CY7C1041DV33 (13 pages)

- CY62167EV18 (13 pages)

- Perform CY7C1565V18 (28 pages)

- STK11C68-5 (15 pages)

- 7C185-20 (11 pages)

- CY7C1168V18 (27 pages)

- CY7C1318CV18-250BZC (26 pages)

- CY7C1364C (18 pages)

- Perform CY7C1382D (34 pages)

- CY7C106D (11 pages)

- CY14E102N (21 pages)

- CY7C1418AV18 (31 pages)

- enCoRe CY7C638xx (83 pages)

- CY7C1018DV33 (9 pages)

- CY7C1292DV18 (23 pages)

- CY7C130 (19 pages)

- CY7C1424BV18 (30 pages)

- CY62157EV18 (12 pages)

- CY7C1392BV18 (31 pages)

- CY7C1302DV25 (18 pages)

- Perform CY7C1511KV18 (31 pages)

- West Bridge Astoria AN46860 (4 pages)

- CY7C1386FV25 (30 pages)

- CY7C1163V18 (29 pages)

- CY7C1266V18 (27 pages)

- CY7C1334H (13 pages)

- CY7C1018CV33 (7 pages)

- CY62136VN (12 pages)

- AN20639 (3 pages)

- CY7C1338G (17 pages)

- CY7C1462AV33 (27 pages)

- CY7C1145V18 (28 pages)

- STK11C88 (15 pages)

- CY7C1231H (12 pages)

- Perform CY7C142 (15 pages)

- CY14E256L (18 pages)

- STK15C88 (15 pages)

- CY7C1297H (15 pages)

- CY7C1441AV33 (31 pages)

- CapSense CY8C20x36 (34 pages)