6 ulpi signal test points, 7 block diagram, Usb otg connector – Digilent EVB-USB3300-XLX User Manual

Page 4: 3x13 header

EVB-USB3300-XLX User Manual

Revision 0.4 (06-29-07)

SMSC EVB-USB3300-XLX

4

2.6

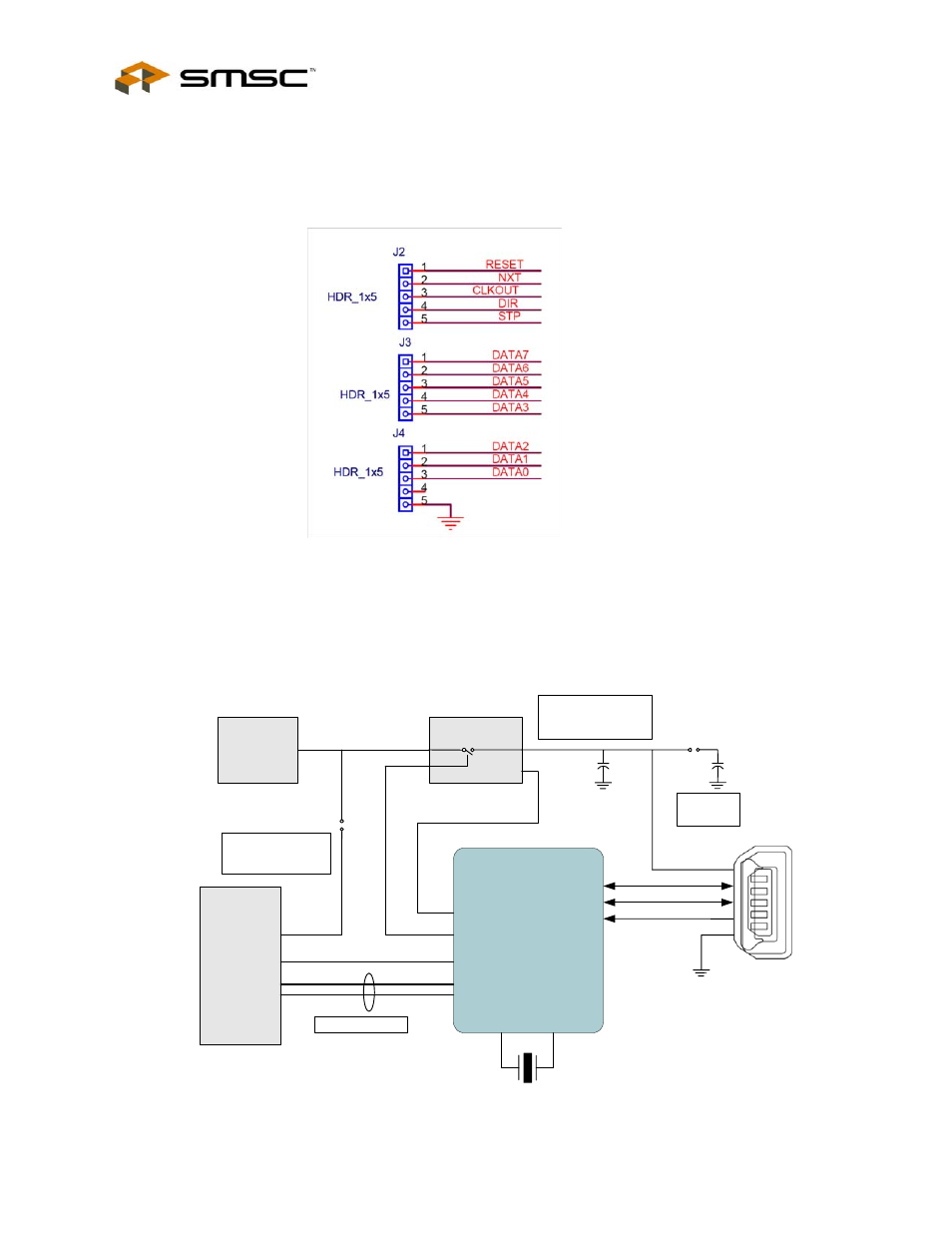

ULPI Signal Test Points

The headers J2, J3 and J4 provide easy access to the ULPI signals, and each pin has a silk screen

label as shown in

Figure 1

.

2.7

Block Diagram

The EVB-USB3300-XLX block diagram shows how the jumpers are used on the board.

Figure 1 ULPI Signal Test Points

Figure 2 EVB-USB3300-XLX Block Diagram

USB3300

J5

5V DC

Input

U1

VBUS

ID

DP

DM

USB OTG

Connector

24 MHz XTAL

3x13

Header

J6

J7

5.6uF

150uF

Install to source +5V

from the FPGA

development system.

VBUS Switch

500 mA current limit

w/ Fault Detection

ONA

FAULTAn

VDD3.3

5V

EXTVBUS

CPEN

VDD3.3

ULPI Signals

DP

DM

ID

ULPI Bus

GND

J7 Install for

Host mode

J1

See also other documents in the category Digilent Hardware:

- 410-282P-KIT (4 pages)

- 410-279P-KIT (26 pages)

- 410-258P-KIT (16 pages)

- 410-138P-KIT (28 pages)

- 410-178P-KIT (22 pages)

- 410-292P-KIT (29 pages)

- 410-274P-KIT (29 pages)

- 410-182P-KIT (22 pages)

- 410-134P-KIT (17 pages)

- 410-183P-KIT (19 pages)

- 410-155P-KIT (12 pages)

- 6015-410-001P-KIT (26 pages)

- 410-087P-KIT (164 pages)

- 410-146P-KIT (4 pages)

- 6003-410-000P-KIT (138 pages)

- XUPV2P (23 pages)

- 410-047-C2P-KIT (3 pages)

- WaveForms (85 pages)

- 410-297P-KIT (25 pages)

- 410-295P-KIT (37 pages)

- 410-296P-KIT (23 pages)

- 410-209P-KIT REV.D (16 pages)

- 410-209P-KIT REV.C (17 pages)

- 410-254P-KIT (17 pages)

- 410-280P-KIT (9 pages)

- 410-202P-KIT (20 pages)

- 410-273P-KIT (24 pages)

- 410-269P-KIT (11 pages)

- 410-216P-KIT (15 pages)

- 410-231P-KIT (4 pages)

- 410-211P-KIT (10 pages)

- 410-262P-KIT (8 pages)

- 410-229P (7 pages)

- 410-242P-KIT (4 pages)

- 6021-210-000P-KIT (27 pages)

- 410-185P-KIT (21 pages)

- 6032-410-000P-BOARD (4 pages)

- 410-174P (17 pages)

- 410-145P (6 pages)

- 210-264P-BOARD (3 pages)

- 6003-210-012P (27 pages)

- 410-236P-BOARD (2 pages)

- 410-163P (1 page)

- 410-097P-KIT (2 pages)

- 410-255P-KIT (1 page)